https://doi.org/10.12677/iae.2022.103026

# 基于FPGA的自适应梯形成形算法的研究

江 环,胡颖睿,马 健

西南民族大学电子信息学院,四川 成都

收稿日期: 2022年8月1日: 录用日期: 2022年9月2日: 发布日期: 2022年9月9日

#### 摘要

梯形成形算法是整形滤波算法中应用最广的。目前的梯形成形技术只能手动调节成形参数,操作复杂且效率低下,为了进一步增强数字脉冲幅度分析技术的便利性,增加成形算法关键参数的自适应算法。先根据原有算法原理在MATLAB SIMULINK中进行初步仿真,采用现场可编程逻辑器件(Field Programmable Gate Array, FPGA)和硬件描述语言(Verilog)完成梯形成形算法的自适应算法,利用Quartus II编写程序,并用ModelSim软件对设计进行功能仿真。通过仿真验证,结果证明设计能够自适应调整梯形成形参数,填补了数字化脉冲幅度分析技术中梯形成形算法的自适应内容。

#### 关键词

梯形成形技术,自适应算法,FPGA

# Research on Adaptive Trapezoidal Shaping Algorithm Based on FPGA

Huan Jiang, Yingrui Hu, Jian Ma

College of Electronic and Information, Southwest Minzu University, Chengdu Sichuan

Received: Aug. 1<sup>st</sup>, 2022; accepted: Sep. 2<sup>nd</sup>, 2022; published: Sep. 9<sup>th</sup>, 2022

#### **Abstract**

Trapezoidal shaping algorithm is the most widely used shape filter algorithm. The current trapezoidal shaping technology can only manually adjust the shaping parameters, which is complicated and inefficient. Enhance the convenience of digital pulse amplitude analysis technology and increase the adaptive algorithm of key parameters of the shaping algorithm. First, carry out preliminary simulation in MATLAB SIMULINK according to the original algorithm principle, use field programmable logic device (Field Programmable Gate Array, FPGA) and hardware description language (Verilog) to complete the adaptive algorithm of trapezoidal shaping algorithm, use Quartus

文章引用: 江环, 胡颖睿, 马健. 基于 FPGA 的自适应梯形成形算法的研究[J]. 仪器与设备, 2022, 10(3): 197-204. POI: 10.12677/jae.2022.103026

II to write the program, and use ModelSim software to design the design perform power simulation. Through simulation verification, the results show that the design can adjust the trapezoidal shaping parameters adaptively, which fills the adaptive content of the trapezoidal shaping algorithm in the digital pulse amplitude analysis technology.

#### **Keywords**

Trapezoidal Shaping Technology, Adaptive Algorithm, FPGA

Copyright © 2022 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0). http://creativecommons.org/licenses/by/4.0/

Open Access

#### 1. 引言

指数衰减信号一般呈现上升快、峰值点窄,拖尾长的特点,导致对该种信号的幅度信息提取难度大。 采用的梯形成形算法的原理则是将难以通过采样得到的峰值点拓宽,使得其更容易被采到。该种算法内 部逻辑较复杂,但优点是幅度信息准确,能控制梯形参数,参数调节灵活,有效减少由于衰减过程导致 基线漂移和脉冲堆积的概率[1],并且只要对控制好算法参数,就能消除弹道亏损[2]。本文提出的基于 FPGA 的自适应梯形成形的算法利用 FPGA 的并行、高速优势,通过代码将最终成形的梯形信号的上升 沿时间、平顶时间、下降沿时间都能确定。并加入了自适应内容,利用输入原信号的特征进行初步计算, 进一步得到成形结果,对比结果的特殊点数据,判断是否还需要进行算法参数调整,如此,经过多次迭 代,最终实现输出顶部平坦的梯形信号。

### 2. 梯形成形算法原理

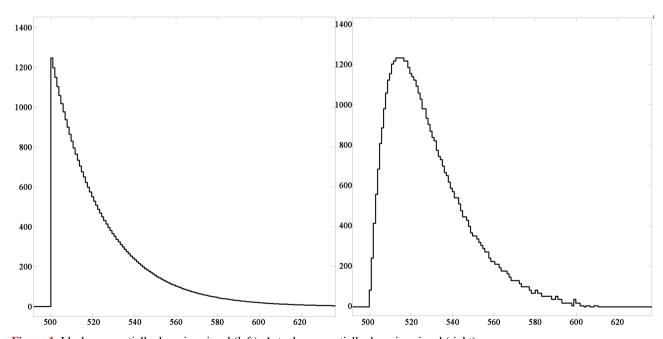

Figure 1. Ideal exponentially decaying signal (left); Actual exponentially decaying signal (right) 图 1. 理想指数衰减信号(左); 实际指数衰减信号(右)

如图 1 所示,无论是理想信号还是实际信号,要准确提取到信号的幅度信息,必须要采到对应的时间点,而指数衰减信号从脉冲到来至衰减至 0 最大只有几个微秒的时间,要在这样的信号中精确采集到峰值点,难度可想而知。

梯形成形算法的目的就是将指数衰减信号滤波成形为上升时间、平顶时间可控等腰梯形。理想研究 对象表达式为:

$$v_i(t) = V_{\text{max}} * e^{-t/\tau} * u(t)$$

(1)

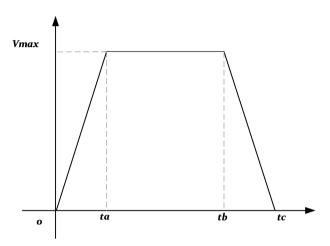

其中, $V_{max}$ 为信号幅度, $\tau$ 为信号衰减时间常数。输出期望信号图形如图 2 所示。

Figure 2. Trapezoidal shaping desired output 图 2. 梯形成形期望输出

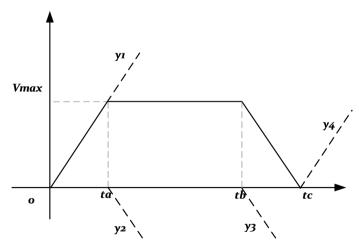

$t_a$  为梯形上升时间, $t_b-t_a$  为平顶时间, $t_c-t_b$  为梯形下降时间,梯形成形算法原理如图 3,其表达式为:

$$v_o(t) = \sum_{j=1}^4 y_j(t) \tag{2}$$

$$y_{1}(t) = \frac{V_{\text{max}}}{t_{a}} tu(t), y_{2}(t) = -y_{1}(t - t_{a}), y_{3}(t) = -y_{1}(t - t_{b}), y_{4}(t) = -y_{1}(t - t_{c})$$

(3)

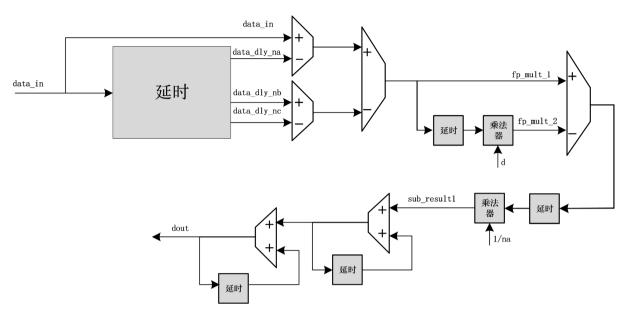

Figure 3. Trapezoidal shaping algorithm 图 3. 梯形成形算法

对等式(1)、等式(2)离散化,再经过Z变换后做商可得到整个系统的传递函数H(z):

$$\frac{V_o}{V_i} = H(z) = \frac{z^{-1} (1 - z^{-n_a}) (1 - z^{-n_b}) (1 - dz^{-1})}{n_a (1 - z^{-1})^2}$$

(4)

其中, $n_a$ 为上升沿采样点数, $\left(1-z^{-n_a}\right)$ 产生上升沿; $n_b$ 为平顶部分采样点数, $\left(1-z^{-n_b}\right)$ 产生下降沿;

$$d = e^{\frac{-T_s}{\tau}}$$

,  $T_s$  取 1,  $(1-dz^{-1})$ 用于去除拖尾;  $\frac{z^{-1}}{n_a}$ 用于匹配时间和幅度;  $\frac{1}{\left(1-z^{-1}\right)^2}$  为反馈部分,用于产生

梯形形状;将等式(4)经 Z 逆变换转换到时域后,可得最终算法的时域表达式:

$$y(n) = 2y(n-1) - y(n-2) + \frac{1}{n_a} * \{ [x(n-1) - x(n-n_a-1) - x(n-n_b-1) + x(n-n_c-1)] - d[x(n-2) - x(n-n_a-2) - x(n-n_b-2) + x(n-n_c-2)] \}$$

(5)

#### 3. 自适应研究

1994年。美国的研究员 Valentin. T. Jordanov 利用 ADC 进行信号的模数转换[3],实现数字化指数衰减信号的滤波过程。西班牙的 Alberto Regadio 等人主要研究了 ADC 采样频率与梯形成形平顶之间对应关系,提出了实时化自适应数字滤波成形方法 [4];国内关于梯形成形自适应的技术主要是成都理工大学王敏提出双重遗忘法实现了脉冲的基线恢复[5] [6]、同校的凡小红实现了基于 LMS 算法的自适应梯形成形算法[7]。

通过对市面上相关产品的调研,发现对于梯形成形的部分均未实现对不同输入信号进行自适应梯形成形的功能。根据等式(5)可知,算法中参数只有  $n_a$ 、 $n_b$ 、d 三个,一般来说对于不同输入,我们需要控制输出梯形的上升时间和平顶时间一致,即自适应参数只有 d。

由于输入信号的  $\tau$  值不同,直接导致与之有数学关系的 d 值不同,而传统产品均是在已知输入信号特征的情况下,通过程序来选择算法内设的参数。这种方法的主要弊端有两个,一方面,需要存入足够多的参数用于应对不同的输入信号;另一方面,当一种输入信号随着环境改变而发生波形变化时,显而易见,固定参数无法处理这种情况。此时,就需要有一种算法能根据波形实时特征及时调整成形算法参数 d。在设计中通过对脉冲衰减阶段进行采样,采集相邻两个点的数据做商,结果即为 d,推导过程如下:

$$v_i(n) = V_{\text{max}} * e^{-\frac{n}{\tau}} * u(n) = V_{\text{max}} * d^n * u(n)$$

(6)

$$v_i(n-1) = V_{\text{max}} * d^{n-1} * u(n-1)$$

(7)

$$v_i(n) - d * v_i(n-1) = V_{\text{max}} * d^n * [u(n) - u(n-1)] = V_{\text{max}} * d^n * \delta(n)$$

(8)

当 $n \neq 0$ 时,可得:

$$\frac{v_i(n)}{v_i(n-1)} = d \tag{9}$$

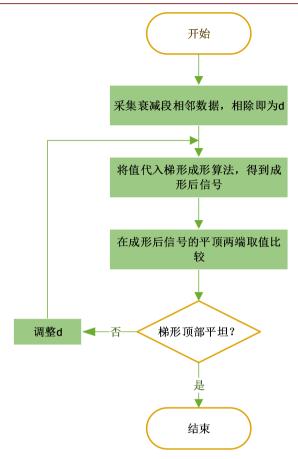

通过求得的 d 值带入梯形成形算法,得到第一次的成形结果,再按照时序在平顶时间位置采数据对比,如果取得的两个数据相差在允许误差范围内,即认为成形完成,d 值为最终成形参数,如果两个数据相差很大,则按照大小关系增大或减小 d 值,再对输出取样,迭代多次,即可得到最终结果,梯形成形自适应流程图如图 4 所示。

**Figure 4.** Trapezoidal shaping adaptive flowchart **图 4.** 梯形成形自适应逻辑

#### 4. 总体设计

#### 4.1. ADC 量化模块

设计的输入信号为连续信号,先在  $40\,$  MHz 时钟下经过  $12\,$  位 ADC 采样量化,并将量化后的数据送进 FPGA 中存储器中,以供读取。

#### 4.2. 离散化数据存取

由于 FPGA 片内时钟频率为 100 MHz, 远高于 ADC 采样时钟频率,为使得数据存取过程不发生丢失,需要对数据进行异步时钟读取,采用典型的乒乓操作存取数据,存取方式如图 5 所示,通过交叉控制两片双时钟 RAM 读写使能进行存取,写入时钟为 40 MHz,读出时钟为 100 MHz。

**Figure 5.** Schematic diagram of ping-pong operation **图 5.** 乒乓操作示意图

#### 4.3. 梯形成形模块

**Figure 6.** Trapezoid shaping module flow chart **图 6.** 梯形成形模块流程图

观察系统函数 H(z)的表达式不难发现,此函数具有输出反馈环节,是一个无限脉冲响应(Infinite Impulse Response, IIR)数字滤波系统。为了降低系统设计的复杂度,方便信号的流水线计算,避免整形和浮点数之间转换误差的积累,故选择如图 6 所示级联结构来实现,仿真中关键信号介绍如表 1 所示。通过仿真发现,对于线性移不变系统,改变各级联系统的顺序不会影响最终输出的梯形信号,但由于在 FPGA中具体实现中存在误差与有限字长效应(主要是把系数 d 用有限位二进制表示时产生的量化效应),所以必须考虑系统的分解方式与级联顺序。另外对于 FPGA 内部的浮点数乘法和除法需要特别注意,一般乘法 IP 核的计算延时(Output Latency)为 5 至 11 个周期,而浮点数的除法 IP 核一般有 14 至 33 个周期的延时,为了提高整个系统的实时性,尽量减少除法器 IP 核的调用。由于模块输入信号为 12 位整形数据,而参数 d 一般为 0 到 1 的浮点数,为了节省资源、优化时序,故整个模块数据类型为整形 - 浮点数 - 整形,在初期将整形运算均完成,将结果转换成浮点数运算,最后再转换成整形,完成反馈及最终输出。

Table 1. Introduction of related signals 表 1. 相关信号介绍

| 信号名称        | 数学表达式                                                                     |  |

|-------------|---------------------------------------------------------------------------|--|

| data_in     | 输入的离散数据                                                                   |  |

| data_dly_na | $data_i$ n 延时 $n_a$ 个周期                                                   |  |

| data_dly_nb | $data_i$ n 延时 $n_b$ 个周期                                                   |  |

| data_dly_nc | data_in 延时 $n_c$ 个周期, $n_c = n_a + n_b$                                   |  |

| fp_mult_1   | $\left(1-z^{-n_a}\right)\!\!\left(1-z^{-n_b}\right)$                      |  |

| fp_mult_2   | $(1-z^{-n_a})(1-z^{-n_b})(1-dz^{-1})$                                     |  |

| sub_result1 | $\Big[z^{-1}ig(1-z^{-n_a}ig)ig(1-z^{-n_b}ig)ig(1-dz^{-1}ig)\Big]\Big/n_a$ |  |

| dout        | 最终输出的梯形信号                                                                 |  |

|             |                                                                           |  |

# 5. 仿真测试

仿真部分共分为两个部分,第一部分为 MATLAB 仿真,以理想信号作为输入验证算法的正确性;第二部分为实际信号输入,先通过 MATLAB 仿真,再利用 QUARTUS II 编程和 ModelSim 仿真软件验证自适应功能。

# 5.1. 理想信号 MATLAB 仿真

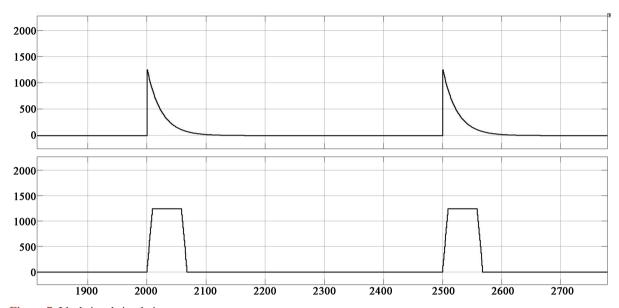

Figure 7. Ideal signal simulation

图 7. 理想信号仿真

由<mark>图 7</mark> 可知,根据参考文献及相关推导得出的梯形成形公式能够成功将理想的指数衰减信号滤波成形为梯形信号。

#### 5.2. 实际信号 MATLAB 仿真

Figure 8. Real signal simulation

图 8. 真实信号仿真

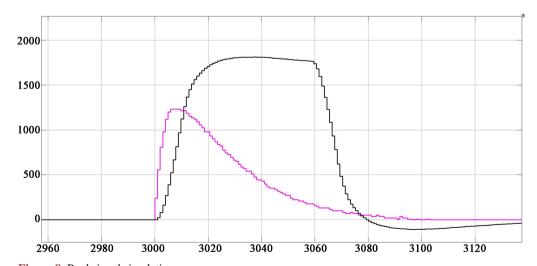

利用示波器将实际信号采集下来,存入 ROM 中,利用编写好的自适应算法,直接将最终的参数 d 的值作为常数代入仿真,最终真实信号的最大值为 1233,而最后成形的梯形平顶高度为 2030,根据仿真结果可见,经过梯形成形后的信号,幅度增长较大,平顶明显,梯形特征清晰,图 8 结果证明,真实信号可以成功成形成梯形。

#### 5.3. 实际信号 ModelSim 仿真

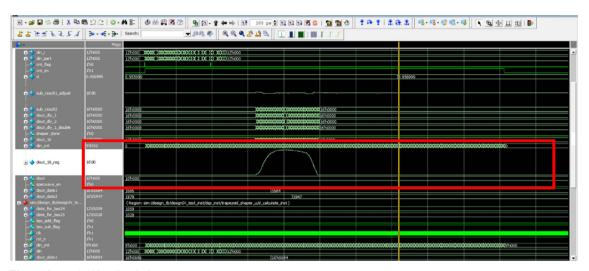

Figure 9. ModelSim simulation

图 9. ModelSim 仿真

由仿真输出图 9 可见,数据与 MATLAB 输出波形形状吻合,对比数据后,证明数据大小。结果证明设计正确。

#### 6. 结论

本文利用 MATLAB 软件 SIMULINK 工具仿真实现了传统梯形滤波成形算法,分析了级联环节的作用,通过增加负反馈环节自适应的调节成形参数以实现梯形输出,增强了该算法的环境适应性;利用 Quartus II 编写 Verilog 代码,通过级联方式简化 FPGA 处理过程,提高了系统的实时性;通过对实际脉冲信号进行采集,经 ModelSim 仿真得到的测试结果与 MATLB 仿真结果大体一致,也证实了本设计提出的算法是可行的,对梯形成形算法在 FPGA 上的应用研究具有一定参考价值。

#### 参考文献

- [1] 肖无云, 魏义祥, 艾宪芸. 数字化多道脉冲幅度分析中的梯形成形算法[J]. 清华大学学报(自然科学版), 2005, 45(6): 810-812.

- [2] 李京伦, 肖无云, 艾宪芸. 新型数字多道脉冲幅度分析器设计[J]. 核电子学与探测技术, 2018, 38(3): 387-393.

- [3] Jordanov, V.T., Knoll, G.F., Huber, A.C. and Pantazis, J.A. (1994) Digital Techniques for Real-Time Pulse Shaping in Radiation Measurements. *Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment*, 353, 261-264. https://doi.org/10.1016/0168-9002(94)91652-7

- [4] Regadío, A., Sánchez-Prieto, S., Prieto, M. and Tabero, J. (2014) Lmplementation of a Real-Time Adaptive Digital Shaping for Nuclear Spectroscopy. *Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment*, 735, 297-303. https://doi.org/10.1016/j.nima.2013.09.063

- [5] 王敏. 数字核能谱测量系统中滤波与成形技术研究[D]: [博士学位论文]. 成都: 成都理工大学, 2011.

- [6] 卢炜煌. 核脉冲信号数字成形方法研究与性能分析[D]: [硕士学位论文]. 南昌: 东华理工大学, 2019.

- [7] 凡小红. 自适应算法在数字核脉冲滤波成形的应用[D]: [硕士学位论文]. 成都: 成都理工大学, 2015.