# 内窥镜用图像传感器设计

皮常明1,2,何学红1,曾 夕1,蒋亮亮1

<sup>1</sup>上海集成电路研发中心,上海 <sup>2</sup>复旦大学集成电路与微纳电子创新学院,上海

收稿日期: 2025年6月30日; 录用日期: 2025年8月20日; 发布日期: 2025年8月28日

#### 摘要

本文采用55 nm工艺,设计了一款图像传感器芯片,图像传感器分辨率为400\*400。芯片面积仅为1 mm\*1 mm,并且直接将镜头做到芯片上,实现了小型化的图像传感器模组,可用于人体内组织和器官检测的内窥镜。测试结果表明:所设计的图像传感器可以实现高灵敏度,低噪声,高动态范围,满足人体内窥镜的应用要求。

#### 关键词

图像传感器,内窥镜

# **Design of CMOS Image Sensor Used for Endoscope**

Changming Pi<sup>1,2</sup>, Xuehong He<sup>1</sup>, Xi Zeng<sup>1</sup>, Liangliang Jiang<sup>1</sup>

<sup>1</sup>Shanghai Integrated Circuit Research and Development Center, Shanghai

<sup>2</sup>College of Integrated Circuit and Micro-Nano Electronics, Fudan University, Shanghai

Received: Jun. 30<sup>th</sup>, 2025; accepted: Aug. 20<sup>th</sup>, 2025; published: Aug. 28<sup>th</sup>, 2025

#### **Abstract**

This paper designs an image sensor chip based on 55 nm process. The image sensor has a resolution of  $400 \times 400$ , and the chip area is only 1 mm  $\times$  1 mm. The lens is directly integrated onto the chip to achieve a miniaturized image sensor module, which can be used in endoscopes to detect human internal tissues and organs. The test results show that the designed image sensor can achieve high sensitivity, low noise, and a high dynamic range, meeting the application requirements of human endoscopes.

#### **Keywords**

**CMOS Image Sensor, Endoscope**

文章引用: 皮常明, 何学红, 曾夕, 蒋亮亮. 内窥镜用图像传感器设计[J]. 传感器技术与应用, 2025, 13(5): 729-737. DOI: 10.12677/jsta.2025.135071

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

# 1. 引言

人体组织存在各种细小的通道,如食道,肠道,泌尿管道等,而这些组织在人生的不同时期,需要进行检测以预防疾病的发生,或者已经发生了病变,需要诊断确定的原因,医学内窥镜在这些检查中起到至关重要的作用。但是由于这些人体组织和器官通道一般比较狭窄,所以需要内窥镜的体积较小,能够在人体组织器官通道内进出。而图像传感器实现的内窥镜则在这个领域中发挥了巨大的作用。由于人体组织狭小,所以对图像传感器的分辨率要求不高,400\*400的分辨率已经能够实现较好的成像效果,同时,由于内窥镜和器官壁较近,所以对应的物距较小,一般是 3 mm~20 mm 的范围。由于芯片只有 1 mm\*1 mm,为了封装的小型化考虑,芯片只有四个封装管脚,分别是电压管脚、地管脚、两个数据管脚,其中,两个数据管脚为 LVDS 数据差分输出端口和 IIC 两个通信端口复用。同时由于人体内,组织一般也比较长,如肠道,有 1.5 m 左右,所以也需要芯片能够实现长距离的传输。

# 2. 图像传感器架构和基本原理

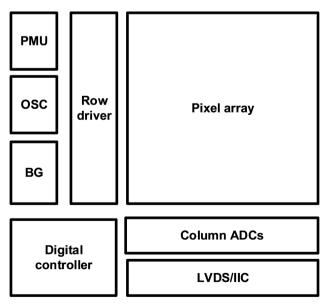

本论文高集成度、四个管脚的封装方案,设计实现了一款内窥镜用图像传感器[1][2]设计架构如图 1 所示。主要包括,pixel array,感光像素阵列; Row driver,行驱动模块,用于实现 pixel array 的逐行控制和读取; PMU (power management unit),为像素提供高低电平; OSC (oscillator),内部时钟发生器; BG (bandgap),为其他模块提供基准电压; column ADCs,用于将像素输出的模拟信号转换为数字信号; LVDS/IIC,节约管脚,两个模块复用管脚,LVDS 实现数据输出传输,IIC 实现芯片寄存器控制和曝光时间,增益等功能配置; digital controller,数字控制模块,用于实现这个芯片的状态切换,曝光,处理,读出,配置等有序配合。

Figure 1. The sensor system architecture **图** 1. 图像传感器系统架构

#### 3. 芯片设计和实现

根据芯片系统架构,对图像传感器中的关键模块进行设计和介绍,主要是 pixel array 电路设计, LVDS/IIC 复用设计,以及芯片工作状态切换控制模块。

# 3.1. 芯片工作状态控制

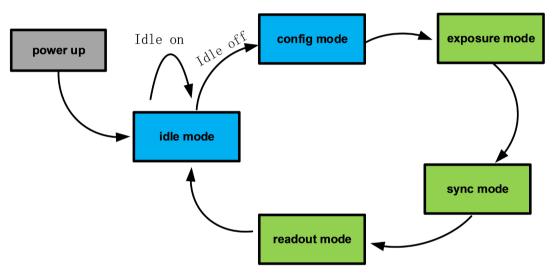

根据图像传感器的原理,图像传感器一般处于 idle 状态(idle mode),配置状态(config mode),曝光状态(exposure mode),同步状态(sync mode)和数据输出状态(readout mode)。Idle 状态:芯片上电后,处于待配置状态;配置状态:用于配置图像传感器的基本参数,包括曝光时间,增益等配置。曝光状态:芯片中像素处于曝光状态;同步状态:由于数据是通过 LVDS 输出,主要是配置同步帧头和行头,为后端 FPGA 接收做同步,实现数据接收准备;数据输出状态或者读出状态:用于实现数据的输出。数据输出结束后,芯片重新返回 idle 模式。对于 IIC 和 LVDS 数据接口来说,在 idle 状态和配置状态下,接口工作在 IIC 模式,在曝光状态,同步状态和数据输出状态下,接口处于 LVDS 模式。基本状态流程图如图 2 所示。

Figure 2. The chip working state flow **图** 2. 芯片工作状态图

#### 3.2. 像素阵列设计实现

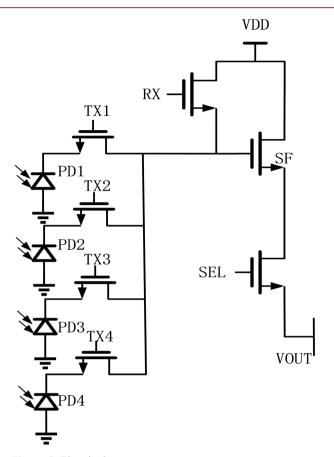

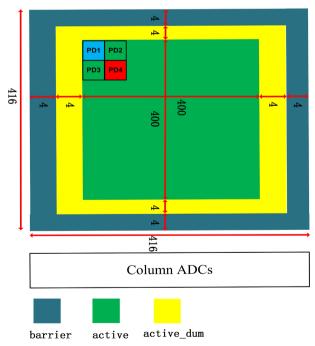

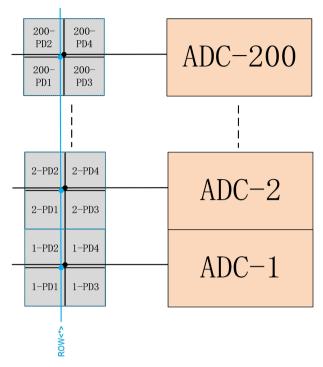

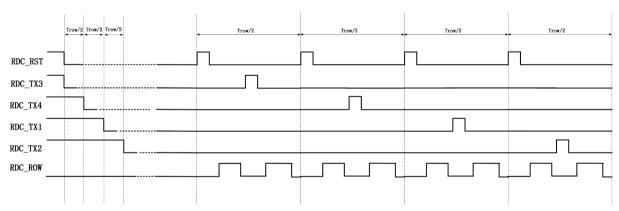

像素阵列是图像传感器的核心模块,由于系统对芯片的尺寸要求较高,所以本设计的像素阵列为400\*400,像素大小为1.12 um,为了增加感光度,采用了BSI (backside-illuminated)技术。基本的像素结构为4T结构,通过相关双采样技术(CDS)有效降低了像素输出的读出噪声和固定图形噪声(FPN),同时像素采用四合一的像素结构以降低管子的占比,从而提高PD (photodiode)的填充率,增加PD 感光特性。图3 为基本的像素结构[2]-[4]。图4 为像素阵列示意图,包含400\*400有效像素、四周4行/列用于保证有效像素制造一致性的dummy像素、以及四周4行/列用于隔离保护的barrier像素。为了实现彩色成像,集成了bayer格式的彩色滤镜。为了进一步提升感光度,每个像素上还集成了微透镜。像素跟列级ADC电路的连接示意图见图5所示,2\*2的像素阵列由1个行选ROW信号控制,每2列像素对应1列ADC电路,所以400\*400有效像素阵列对应200列ADC电路。像素工作时序图见图6所示,每个像素读出占半行时间(Trow/2),2\*2像素全部读出需2行[5]-[7]时间。

Figure 3. The pixel structure 图 3. Pixel 结构

Figure 4. The pixel array diagram 图 4. Pixel 阵列示意图

Figure 5. The pixel connection diagram 图 5. Pixel 连接示意图

Figure 6. The pixel timing diagram 图 6. 像素工作时序示意图

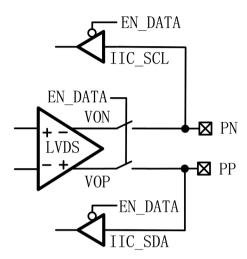

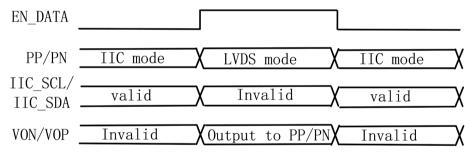

#### 3.3. LVDS/IIC 分时复用 IO 设计

由于芯片面积较小,封装对体积要求严格,需要管脚尽量少,所以采用数字格式输出,LVDS 接口和芯片控制配置接口采用分时复用的方式。在配置芯片过程中,LVDS 输出接口断开。当 LVDS 数据输出时,IIC 的端口无效,实现分时复用的效果,节约芯片管脚。对应电路和控制时序说明如图 7、图 8 所示,IIC 的输入输出端口 IIC\_SCL 和 IIC\_SDA 分别和 LVDS 模块的 VON 和 VOP 经开关后连接在一起。EN\_DATA 为使能信号,控制对应模块是否工作以及输出状态。当 EN\_DATA 为低时,输出端口PP 和 PN 分别与 IIC\_SDA 和 IIC\_SCL 时序一致,LVDS 对应的输出与芯片输出端口 PP、PN 断开,这样 IIC 模块处于工作状态,可以进行芯片配置,寄存器读出等操作。当 EN\_DATA 为高时,IIC 处于无效状态,LVDS 的输出 VON 和 VOP 对应的时序直接输出到 PN 和 PP,实现数据输出。同时为了保证

芯片的启动,在 idle 状态下,接口处于 IIC 模式,这样,芯片可以进行配置,同时可以通过配置切换到 LVDS 输出模式,当时 LVDS 数据输出在一帧结尾时,会输出特定字符,芯片外部接收端通过此特定字符判断此时一帧数据已完成输出,随后,芯片自动切换为 idle 模式,等待下一次配置或图像传感器数据输出,芯片接收端控制接收端从 LVDS 模式切换为 IIC 模式,并根据需要,选择是否需要进行 IIC 配置。

Figure 7. The LVDS/IIC module multiplex structure 图 7. LVDS/IIC 电路模块复用结构

Figure 8. The LVDS/IIC module multiplex timing 图 8. LVDS/IIC 模块复用时序

Table 1. The LVDS electrical characteristic 表 1. LVDS 电气特性

| Parameter         | Description                                        | Condition                      | Min  | Тур | Max  | UNITS |

|-------------------|----------------------------------------------------|--------------------------------|------|-----|------|-------|

| $V_{\mathrm{OD}}$ | Differential output voltage                        | Steady state, $RL = 120\Omega$ | 36   | 60  | 150  | mV    |

| Voc               | Common mode voltage Steady state, $RL = 120\Omega$ |                                | 1.26 | 1.4 | 1.54 | V     |

| $T_{\rm r}$       | Output slew rate of rising edge                    |                                |      | 3   |      | ns    |

| $\mathrm{T_{f}}$  | Output slew rate of falling edge                   |                                |      | 3   |      | ns    |

| IData+, Data-     | LVDS output current                                |                                | 300  | 500 | 600  | uA    |

| Data rate         |                                                    |                                |      | 84  |      | Mbps  |

LVDS 模块电气特性见表 1,为在模组端长距离走线情况下仍能实现高速数据输出,差分电压幅度较常见的 LVDS 差分电压小,典型条件下约 60 mV,为匹配不同走线长度的应用情况,输出差分电压幅度

可配置的最大范围为  $36 \text{ mV} \sim 150 \text{ mV}$ 。为满足全芯片 40 fps 的帧率要求,LVDS 的工作速度典型值为 84 Mbps。

## 4. 芯片模组应用

1 mm\*1 mm 这么小尺寸的芯片,配套的 lens 加工也是个难点。Lens 的设计,根据一次性内窥镜使用的技术要求及芯片本身特点,进行了定制化开发,采用 WLO 压印工艺,通过跟芯片的紧贴合以及喷漆遮黑加工,实现了内窥镜模组中小型化和遮光的需求,如图 9 所示。

Figure 9. The photo of the chip module cross-sectional 图 9. 芯片模组横截面照片

芯片模组(lens + 芯片)的后端应用,根据芯片本身的特点,进行了配套开发:

1) 根据 LVDS/IIC 分时复用的特点,通过分时开关切换,按时序分离出 LVDS 和 IIC,同时 LVDS 信号经过运放放大后,输入到后端 FPGA。FPGA 可以直接采样 LVDS 信号出图,不需要额外再加一个带 ADC 功能的解码器,应用更加灵活。系统控制示意图如图 10 所示。

Figure 10. The system control diagram 图 10. 系统控制示意图

2) 得益于 LVDS 数字信号抗干扰强的特点,芯片模组的信号传输采用双绞线方式即可。经过上述电路的设计及 FPGA 采集时序的优化,芯片模组传输距离可以稳定跑 6 米长线,且没有竖条纹之类的问题。

#### 5. 测试结果

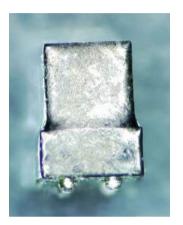

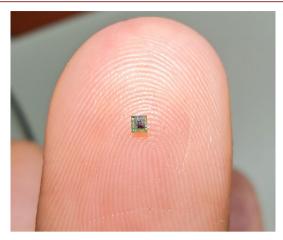

本文采用 55 nm 对芯片进行设计,并测试,同时将镜头做到芯片上,实现图像传感器模组小型化。 图 11 为芯片模组实物图,图 12 为图像传感器的成像效果图。

测试性能指标表 2 所示,测试结果表明: 所设计的图像传感器芯片达到较高的灵敏度,较低的噪声,可以满足内窥镜的应用需求。

Figure 11. The chip physical photo 图 11. 芯片模组实物图

Figure 12. The image output from the system 图 12. 成像效果图

Table 2. The camera module spec 表 2. 图像传感器芯片模组参数

| 事项     | 参数      | 单位  |

|--------|---------|-----|

| 分辨率    | 400*400 | /   |

| 像素大小   | 1.12    | um  |

| 噪声     | <1      | e-  |

| 满阱     | 6000    | e-  |

| 帧率     | 40      | fps |

| ADC 位数 | 10      | bit |

| 物距     | 3~20    | mm  |

| 视场角    | 120     | 度   |

#### 6. 结论

本文设计了一款应用于内窥镜的图像传感器芯片,集成了片内 ADC,并实现了 LVDS 和 IIC 复用端口的设计,芯片端口减少至 4 个端口,满足芯片小型化,高集成度的特点,同时兼顾了性能和应用灵活性,为后端接收和处理提供了便捷的方案。测试结果表明:芯片模组性能优异,满足内窥镜应用的性能需求。

# 参考文献

- [1] Mori, K., et al. (2017) Back Side Illuminated High Dynamic Range 3.0μm Pixel Featuring Vertical p-n Junction Capacitance in A Deep Pinned Photodiode. 2017 International Image Sensor Workshop, Hiroshima, 30 May-2 June 2017, 27.

- [2] Park, J., Park, S., Cho, K., Lee, T., Lee, C., Kim, D., et al. (2021) 7.9 1/2.74-Inch 32mpixel-Prototype CMOS Image Sensor with 0.64<sub>μ</sub> M Unit Pixels Separated by Full-Depth Deep-Trench Isolation. 2021 *IEEE International Solid-State Circuits Conference (ISSCC)*, San Francisco, 13-22 February 2021, 122-124. https://doi.org/10.1109/isscc42613.2021.9365751

- [3] Mori, M., Katsuno, M., Kasuga, S., Murata, T. and Yamaguchi, T. (2004) A 1/4in 2M Pixel CMOS Image Sensor with 1.75 Transistor/Pixel. 2004 *IEEE International Solid-State Circuits Conference*, San Francisco, 15-19 February 2004, 110-111. https://doi.org/10.1109/isscc.2004.1332618

- [4] Goiffon, V., Virmontois, C. and Magnan, P. (2011) Investigation of Dark Current Random Telegraph Signal in Pinned Photodiode CMOS Image Sensors. 2011 International Electron Devices Meeting, Washington, 5-7 December 2011, 8.4.1-8.4.4. https://doi.org/10.1109/iedm.2011.6131514

- [5] Takeuchi, Y., Kunikiyo, T., Kamino, T., Kimura, M., Tanizawa, M. and Yamaguchi, Y. (2015) Investigation of Leakage Current in Pinned Photodiode CMOS Imager Pixel with Negative Transfer-Gate Bias Operation. 2015 International Conference on Simulation of Semiconductor Processes and Devices (SISPAD), Washington, 9-11 September 2015, 76-79. https://doi.org/10.1109/sispad.2015.7292262

- [6] Wang, X., Snoeij, M.F., Rao, P.R., et al. (2004) A CMOS Image Sensor with a Buried-Channel Source Follower. 2008 *IEEE International Solid-State Circuits Conference*, San Francisco, 3-7 February 2008, 62-595.

- [7] Chen, Y., Wang, X., Mierop, A.J. and Theuwissen, A.J.P. (2009) A CMOS Image Sensor with In-Pixel Buried-Channel Source Follower and Optimized Row Selector. *IEEE Transactions on Electron Devices*, 56, 2390-2397. <a href="https://doi.org/10.1109/ted.2009.2030600">https://doi.org/10.1109/ted.2009.2030600</a>