## 针孔缺陷下的全硅介质层同轴硅通孔热应力 仿真分析

#### 章旭然

上海理工大学光电信息与计算机工程学院,上海

收稿日期: 2025年4月26日; 录用日期: 2025年5月19日; 发布日期: 2025年5月27日

## 摘要

文章以同轴硅通孔(Coaxial Through-Silicon Via, C-TSV)的基本三维模型为基础,研究其发生针孔缺陷时的热应力变化。采用有限元分析法,借助热仿真软件COMSOL搭建对应模型,对处于20℃~120℃工作环境下的模型热应力变化进行仿真。将不同温度载荷下针孔缺陷硅通孔应力变化情况与无缺陷同轴硅通孔同等温度条件下的热应力进行对比。实验表明,针孔缺陷将放大硅通孔在高温载荷下的能量释放与应力形变,最终导致C-TSV发生裂纹现象与材料剥离。本研究对缺陷硅通孔进行建模,并且提出了有效抑制该缺陷的措施,填充了对于缺陷同轴硅通孔在应用领域检测与应对方面的空白。

#### 关键词

同轴硅通孔,有限元仿真法,COMSOL,热应力模型,缺陷抑制

# Thermal Stress Simulation Analysis of Coaxial Through-Silicon Via in All-Silicon Dielectric Layer under Pinhole Defect

## **Xuran Zhang**

School of Optical-Electrical and Computer Engineering, University of Shanghai for Science and Technology, Shanghai

Received: Apr. 26<sup>th</sup>, 2025; accepted: May 19<sup>th</sup>, 2025; published: May 27<sup>th</sup>, 2025

#### **Abstract**

Based on the basic three-dimensional model of coaxial through-silicon via (C-TSV), this paper studies

文章引用: 章旭然. 针孔缺陷下的全硅介质层同轴硅通孔热应力仿真分析[J]. 建模与仿真, 2025, 14(5): 779-788. DOI: 10.12677/mos.2025.145433

the thermal stress changes when pinhole defects occur. In this study, the finite element analysis method was used to build the corresponding model with the help of the thermal simulation software COMSOL, and the thermal stress change of the model under the working environment of  $20^{\circ}\text{C} \sim 120^{\circ}\text{C}$  was simulated. The stress changes of the pinhole-defective through-silicon vias under different temperature loads are compared with the thermal stress of the defect-free coaxial through-silicon vias under the same temperature conditions. Experiments show that the pinhole defect will amplify the energy release and stress deformation of the through silicon vias under a high-temperature load, which will eventually lead to the crack phenomenon and material peeling of C-TSV. In this study, the defect through silicon via is modeled, and effective measures to suppress the defect are proposed, which fills the gap in the detection and response of the defect coaxial through silicon via in the application field.

## **Keywords**

Coaxial Through-Silicon Via, Finite Element Simulation Method, COMSOL, Thermal Stress Model, Defect Suppression

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Open Access

## 1. 引言

随着芯片成本的增大和晶体管数量的增多,构建集成电路芯片组面临的技术难度也趋于困难。在此背景下,三维集成电路的发展与应用逐渐成熟[1]。而硅通孔(Through-Silicon Via, TSV)作为三维集成电路的关键组件,构成了芯片间或晶圆间信号连接的通道,给集成电路提供了更高的性能及密度[2]。与此同时,为了避免芯片堆叠结构导致的高集成度所带来的寄生效应,硅通孔衍生出了不同的结构。其中采用同轴结构的硅通孔(Coaxial Through-Silicon Via, C-TSV)不需要额外的接地 TSV,信号传输所产生的电磁场能量只在内外导体之间传输,对信号间的串扰及传输时的损耗具有有效的抑制作用[3]。在高频领域,C-TSV 有着广泛的应用。

然而,C-TSV 在制造过程中受限于良率等因素,容易产生如开路缺陷、针孔缺陷等结构性故障,一定程度上对 3D 封装的高性能、高密度和高可靠性产生影响[4]。C-TSV 本身为具有多层材料结构特征的圆柱体,自 C-TSV 中心向外围硅基底依次分布中心导体、绝缘层、介质层、绝缘层和外围导体。考虑到 C-TSV 的信号传输需求,其中心导体和外围导体通常选用铜来进行填充,而介质层一般选取如 Si 等的低损耗材料,两者之间由绝缘层相隔[5]。然而,此类材料的热膨胀系数(Coefficient of Thermal Expansion, CTE) 相差较大。在制造及应用过程中由于温度变化,C-TSV 本身不同材料产生的热应力互相冲突。同时,针孔缺陷 C-TSV 本身的结构性缺陷也会放大热应力对材料造成的损耗[6]。因此对针孔缺陷 C-TSV 的热应力仿真分析具有充足的必要性。

本文以 C-TSV 的理论模型为基础,通过 COMSOL 软件对针孔缺陷 C-TSV 进行热应力仿真,搭建多物理场应力耦合模型。通过有限元分析法(Finite Element Analysis, FEA)对在 20℃~120℃之间的 C-TSV 绝缘层与中心导体层接触界面的热应力分布特征及变化趋势进行量化分析,并与无缺陷 C-TSV 的热应力解析模型进行对比。最终得出针孔缺陷将导致 C-TSV 中心导体与绝缘层接触部分的应力集中,降低 C-TSV 结构稳定性且加剧热循环过程中的材料损耗,导致结构裂纹开裂与中心导体铜钟子层元素剥离。最后,提出绑定前检测与优化 C-TSV 结构及制造工艺的多种方法,对 C-TSV 针孔缺陷进行抑制。该研究以 C-

TSV 缺陷研究与预防为出发点,对高密度 C-TSV 的可靠性优化与先进封装技术具有指导意义。

#### 2. C-TSV 结构与建模

#### 2.1. C-TSV 基本结构

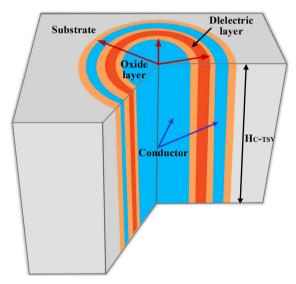

C-TSV 通常为圆柱形,外围导体和中心导体经过介质层和隔离层分隔,共同构成同轴结构[7]。在 C-TSV 应用于高频信号传输时,信号产生的电磁场只存在于内外导体之间,因此可以有效降低电路寄生参数对传输信号的影响。图 1 为一个标准的 C-TSV 简化三维视图,其结构由中心导体、管状介质层、绝缘层及外围导体构成,放置于外部的硅衬底中。中心导体与外围导体作为信号传输路径,管状介质层提供电气隔离和机械支持,负责抑制 C-TSV 工作时的材料损耗,各个结构之间用绝缘层隔离开[8]。在热力学方面,因为 C-TSV 本身的高密度结构特征,其热应力问题会显著影响其可靠性和性能[9]。

Figure 1. The basic structure view of C-TSV 图 1. C-TSV 基本结构视图

C-TSV 基本制造材料如表 1 所示,本文所用中心导体及外围导体选取金属 Cu 材料,管状介质层选用高电阻性材料 p 型硅(Poly-silicon),而绝缘层则采用  $SiO_2$  材料,这些材料工业生产便利,性能优秀的同时成本也较低。C-TSV 的电特性由其导体、介质层、本身的几何结构等决定,本文研究的 C-TSV 结构参数如表 1 所示,为广泛应用于工业生产的标准结构。

Table 1. Structural parameters of C-TSV 表 1. C-TSV 几何结构参数

| Name                | Material        | Parameters                                |  |

|---------------------|-----------------|-------------------------------------------|--|

| Coaxial TSV         | /               | Height = $50 \mu m$ , Radius = $10 \mu m$ |  |

| Center Conductor    | Copper          | Thickness = $5 \mu m$                     |  |

| Outer Conductor     | Copper          | Thickness = $2 \mu m$                     |  |

| Tubular Dielectrics | Polysilicon     | Thickness = $2.8 \mu m$                   |  |

| Isolation Layers    | Silicon Dioxide | Thickness = $0.1 \mu m$                   |  |

| Substrate           | Silicon         | $Length=40\mu m,Width=40\mu m,$           |  |

## 2.2. 针孔缺陷 C-TSV 结构特征

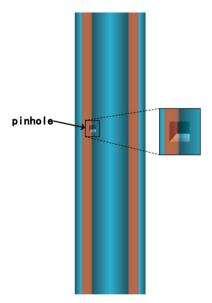

由于 C-TSV 的制作过程复杂,需要的关键技术较多,制作过程中良率较低,而针孔缺陷为常见缺陷的一种。工艺制作不完善、材料本身特性及环境因素都有可能造成 C-TSV 针孔缺陷的生成。比较典型的有介质层沉积时的等离子体化学气相沉积(PECVD)参数失配、原子层沉积(ALD)台阶覆盖率不足、电镀层填充过程中底部铜沉积速率异常,以及阻挡层阴影效应也会造成绝缘层处产生空隙通道。最后,后道退火过程中的热机械应力耦合导致的界面剪切应力、晶圆减薄变形导致的 C-TSV 周围硅基体错位等同样会导致 C-TSV 产生针孔缺陷。综上,C-TSV 针孔缺陷作为制作过程中的典型工艺诱导缺陷,其发生率高达12%~18%,对 C-TSV 热机械可靠性及信号传输性能等都会造成严重威胁,属于 C-TSV 生产制造过程中的关键控制因素。目前针对 C-TSV 进行针孔缺陷检测的方法多为绑定前检测,具体有环振荡器检测、探针检测、光学显微镜检测等等[10]。然而此类缺陷检测法仍有低检测便携度和高成本的限制,因此建立精确有效的 C-TSV 热仿真模型是开展 C-TSV 缺陷检测的必由之路。图 2 为针孔缺陷 C-TSV 的理论示意图,空隙部分对 C-TSV 热力学特性的影响只在于其空隙边缘而与具体的空隙外形无关,出于仿真的可靠性考虑将其设置为一个规则的长方体开口,其长宽高均设置为 2 μm,从中心导体 Cu 穿过绝缘层延伸至硅基介质层。其余几何参数与本文选用的标准 C-TSV 几何参数一致。

Figure 2. C-TSV structure diagram with pinhole defects 图 2. 针孔缺陷 C-TSV 结构图

#### 2.3. C-TSV 的热力学特征参数

C-TSV 一般选用 Cu 作为中心导体及外围导体材料,其具有弹性和塑性双重特性。在其受到外力作用时会发生形变,而当外力消失时形变并不完全恢复,无法恢复的部分就称为塑性形变。当 C-TSV 工作时,随着外部温度载荷的变化引起 Cu 的形变,由于绝缘层及硅基介质层的约束其形变受到限制,C-TSV内部产生热应力。

对 C-TSV 的应力分析通常采用微元法,当材料所受应力小于屈服强度时,由外力产生的应变遵守广义胡克定律,材料处于弹性阶段。应力可以如下表示:

$$F = k(x_1 - x_0) = k\Delta x \tag{1}$$

其中 k 为劲度系数/(N/m),  $x_1$ 、 $x_0$  为形变量, F 即为对应的应力。

引入热膨胀系数后可知三个轴向的应变可以如下所示:

$$\mathcal{E}_{x} = \mathcal{E}_{y} = \mathcal{E}_{z} = \alpha T \tag{2}$$

$\varepsilon$  代表不同轴向的正应变, $\alpha$  为物体的热膨胀系数,T 代表温度的变化量。应力应变和温度变化呈正相关,其中  $\alpha$  在不同温度下数值也会发生小幅度变化。

将杨氏模量 E 和泊松比 v 引入,物理的热弹性方程为:

$$\begin{cases} \varepsilon_{x} = \frac{1}{E} \left[ \sigma_{x} - v \sigma_{y} + \sigma_{z} \right] + \alpha \Delta T \\ \varepsilon_{y} = \frac{1}{E} \left[ \sigma_{y} - v \sigma_{x} + \sigma_{z} \right] + \alpha \Delta T \\ \varepsilon_{z} = \frac{1}{E} \left[ \sigma_{z} - v \sigma_{y} + \sigma_{x} \right] + \alpha \Delta T \end{cases}$$

$$\begin{cases} \gamma_{xy} = \frac{2(1+\nu)}{E} \tau_{xy} \\ \gamma_{xz} = \frac{2(1+\nu)}{E} \tau_{xz} \\ \gamma_{yz} = \frac{2(1+\nu)}{E} \tau_{yz} \end{cases}$$

$$(3)$$

$\gamma_{xy}$ 、 $\gamma_{xz}$ 、 $\gamma_{yz}$  为剪切应力,该方程描述了固体不同方向上的热弹性应力。其值受到温度、杨氏模量、 泊松比等材料特性的共同影响。

## 3. C-TSV 热应力仿真

C-TSV 的工艺生产涉及多道精密加工步骤,且工艺参差和参数波动等都会加大 C-TSV 的测量及评估成本。并且,在目前的 C-TSV 实时应用过程中仍缺乏有效的无损精确检测手段。因此,现阶段对 C-TSV 在应用时的热应力演化特性的表征,主要依赖于仿真模拟技术。本文采用有限元法(Finite Element Method, FEM)对 C-TSV 及针孔缺陷 C-TSV 进行热应力仿真,系统分析了在 20℃~120℃不同温度载荷下的热应力分布特征。并且依据 von Mises 应力准则,预测针孔缺陷 C-TSV 是否会导致界面分层及中心导体元素剥离等风险,为工艺优化提供了理论基础。

#### 3.1. C-TSV 的有限元模型仿真

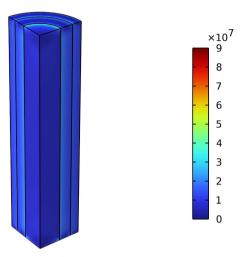

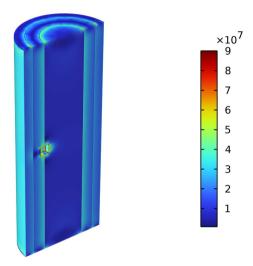

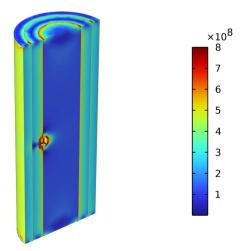

本文使用热仿真软件 COMSOL 对 C-TSV 进行仿真。C-TSV 是十分标准的对称模型结构,选取四分之一或二分之一模型确保精确度的同时提高仿真效率。为了充分模拟 C-TSV 在硅基圆盘中的受热情况,仿真时在外围施加固定约束模拟硅基衬底,截面内部则施加径向和轴向的位移约束,将 C-TSV 中心点设置为固定无位移约束。此时的仿真网格设置为 0.1 μm,在保证仿真效率的情况下提高了仿真精准度。仿真时分别设置 C-TSV 的各项材料层系数,其几何参数设置与上文设置的 C-TSV 几何参数保持一致,热力学参数严格按照表 2 所示,这些参数分别表明了材料抵抗形变的能力、横向变形系数及随温度改变的体积变化能力。鉴于 C-TSV 被广泛应用于高频集成电路中会承受周期性热机械载荷,故本文仿真将初始环境温度设为 20℃,施加持续的升温载荷直到环境温度达到 120℃,整体 C-TSV 模型为均匀受热,观测其热应力仿真数据。图 3 为标准的全硅介质层 C-TSV 在常温环境下的三维建模,图 4 为其被施加了升温载荷至 120℃时的热应力分布图。

**Table 2.** Thermodynamic parameters of C-TSV at standard ambient temperature **表 2.** 标准环境温度下 C-TSV 的热力学参数

| 标准材料         | 杨氏模量/GPa | 泊松比  | 热膨胀系数/10 <sup>-6</sup> ·K <sup>-1</sup> |

|--------------|----------|------|-----------------------------------------|

| Cu           | 117      | 0.31 | 17.7                                    |

| ${ m SiO_2}$ | 71.7     | 0.21 | 0.5                                     |

| Si           | 130      | 0.28 | 2.36                                    |

Figure 3. The stress distribution map of C-TSV at room temperature 图 3. C-TSV 常温下的应力分布图

Figure 4. The stress distribution map of C-TSV at 120°C 图 4. C-TSV 在 120°C 下的应力分布图

根据图示信息可知,在常温环境下 C-TSV 各层应力较小。而在高温环境下,C-TSV 应力分布呈典型的梯度分布特征。由于中心导体 Cu 与介质层的热膨胀系数(CTE)差距较大,径向应力会集中在 Cu 导体外围界面处产生剥离应力,若剥离应力过高则会引发界面裂纹。此时绝缘层充当应力缓冲的作用,较低的杨氏模量使其易于发生弹性形变,向硅基衬底传递受到的应力。从热膨胀系数的角度,SiO<sub>2</sub> 绝缘层 CTE介于中心导体与介质层之间,中心导体产生的应力梯度传递。因此,具有完整绝缘层的 C-TSV 在高温载

荷下有着良好的热机械可靠性,保证了C-TSV的热循环寿命。

#### 3.2. 针孔缺陷 C-TSV 的有限元仿真

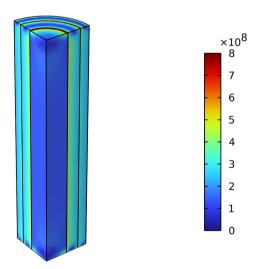

C-TSV 的针孔缺陷主要发生在绝缘层结构,由于 C-TSV 的同轴特性,中心导体与介质层间、外围导体与介质层间都有可能发生针孔缺陷。由于外围导体与硅基衬底相接,仅起到信号引导接地的作用,所以该处的针孔缺陷对 C-TSV 电特性与热力学特性影响较低。目前所称的针孔缺陷通常指中心导体与介质层之间绝缘处发生的针孔缺陷。该缺陷的几何特征表征为绝缘层与中心导体间出现互相连通的空隙。图 5 为针孔缺陷 C-TSV 的 1/2 有限元仿真模型,在绝缘层添加了空气空洞,受热方式为均匀受热,空洞内部设置为材料层固定约束,对其施加升温载荷至 120℃。图 6 为该仿真模型在 120℃环境温度下的热应力仿真模型,选取受热应力影响较为集中的中心导体与介质层交界界面,记录其热仿真数据。

**Figure 5.** Stress distribution of C-TSV with pinhole defects at room temperature **图 5.** 针孔缺陷 C-TSV 的常温应力分布图

Figure 6. The stress distribution of C-TSV with pinhole defects at 120°C 图 6. 针孔缺陷 C-TSV 在 120°C 下的应力分布图

在 120℃的环境温度下,针孔缺陷 C-TSV 出现明显的非均匀性热应力分布。无缺陷 C-TSV 受高温载荷时呈现的梯度分布的应力集中在导体与缺陷空隙边缘的交界部分,绝缘层向外围硅基衬底传递应力的

能力降低。介质层与绝缘层界面应力增大。

## 4. 结果与分析

## 4.1. 热载荷下针孔缺陷 C-TSV 的应力分析

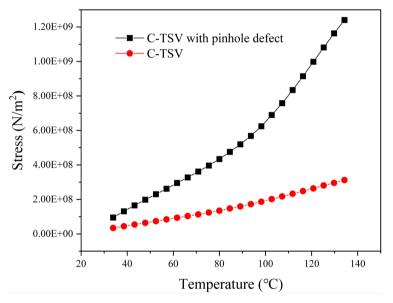

C-TSV 中绝缘层连接中心导体及介质层,介质层采用 Si 材料,与 C-TSV 嵌入的硅基晶圆一致。介质层在减少成本的同时降低 C-TSV 其他材料的层刻蚀难度与沉积难度,受应力影响时可以向硅基衬底分散所受的应力。Si 材料相比绝缘层材料 SiO<sub>2</sub> 有更高的杨氏模量,同时有着更低的热膨胀系数,有一定的抵抗变形能力。中心导体材料 Cu 本身的热膨胀系数较高,施加升温载荷时会产生径向的拉伸应力。这一应力促使 Cu 种子层发生形变,与绝缘层的交界部分产生层面裂纹,而与空洞相接触的部分则会造成 Cu 种子层的剥离,造成中心导体损耗。图 7 为针孔缺陷 C-TSV 与无缺陷 C-TSV 受升温载荷时的应力变化对比,选取的部位为受影响程度最深的绝缘层与导体交界部分。

Figure 7. Temperature-dependent stress changes of two C-TSVs 图 7. 温度相关的两种 C-TSV 应力变化

由图可知,针孔缺陷被施加升温载荷时,其内部热应力与无缺陷 C-TSV 总体保持类似趋势,随着温度的持续升高,内部热应力随之增加。具有针孔缺陷的 C-TSV 在绝缘层空洞与中心导体的交界处,其所受的应力比无缺陷的 C-TSV 更高,出现了明显的热失配现象。在热膨胀和泊松比的共同作用下,空气分散了中心导体受热膨胀时的部分应力,另一部分应力集中作用在缺陷中空隙部分与绝缘层的交界界面,导致该结构承受的应力远大于通常 C-TSV 受热时的应力膨胀。此外,由于绝缘层本身结构完整性的缺失,应力向介质层的传递能力下降,应力集中在整体绝缘层内部,其绝缘层平均应力分布高于 120℃无缺陷 C-TSV。

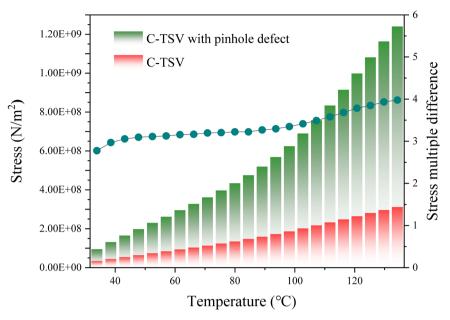

#### 4.2. 热应力集中分布对 C-TSV 的影响

C-TSV 绝缘层是评估 C-TSV 热可靠性评估的重要部分,其在制造及应用过程中起到稳定热应力的作用。然而升温载荷的施加会导致 C-TSV 绝缘层边缘能量释放率上升,当能量释放率超过 Cu/SiO<sub>2</sub>间的界面亲和力时,就会导致不可逆的界面分层开裂现象。图 8 引出两种 C-TSV 在不同温度下的应力比值变化

情况来进行量化分析。

**Figure 8.** Comparison of stress changes of two C-TSVs at different temperatures **图 8.** 两种 C-TSV 在不同温度下的应力对比变化情况

由图 8 可知,升温载荷的施加降低了针孔缺陷 C-TSV 绝缘层抵抗应力形变的能力,环境温度越高,针孔缺陷对 C-TSV 热应力的影响越大。这可能出于工业设计,SiO<sub>2</sub> 层深宽比高于一般 TSV 深宽比,长期工作在高温环境下无法完全抵消 Cu 种子层的残余应力,而针孔缺陷的存在加剧了累积塑性形变对 C-TSV 中心导体热循环寿命的损耗。铜种子层在 Cu/SiO<sub>2</sub> 交界层应力过于集中导致产生裂纹,裂纹随着热循环过程逐渐延伸,最终导致界面开裂。并且由于针孔缺陷的空隙存在,没有足够的绝缘层约束受热膨胀的中心导体铜种子层,铜种子层在径向拉伸应力的作用下产生剥离,对已沉积的铜导体结构产生破坏,C-TSV 的热可靠性和结构完整性下降。

#### 4.3. 应对 C-TSV 针孔缺陷的措施

现今常用的 C-TSV 缺陷应对以预防及检测为主。在设计方面,降低绝缘层深宽比,或者在绝缘层与铜种子层之间设置阻挡层。这两种方法可有效提高绝缘层所能承受的最大界面能量释放率。在前端工序方面,改良制作工艺如精确控制沉积参数及优化介质堆叠技术等,保证绝缘层的均匀沉积。在退火过程中,于120℃至300℃时进行实时检测,抑制铜种子层热循环过程中的热应力问题。此外,降低硅衬底厚度也可以降低绝缘层受到的热形变,但需要考虑阵列中其他 C-TSV 与当前 C-TSV 的等效直径比。同时对 C-TSV 制造时的监控设施进行改良,采用集成光学散射测量法监控 C-TSV 的制造过程。在制造完成之后,通常采用电学检测法,验证其散射参数(s-parameter)或电容电压变化关系等确认 C-TSV 的机械完整性。

#### 5. 结论

本文对 C-TSV 针孔缺陷 C-TSV 的热应力变化情况进行了建模及仿真,并与无缺陷 C-TSV 的热应力仿真模型进行对比。利用 COMSOL 仿真软件模拟了 20℃至 120℃下各材料层热应力的变化趋势。同时,分析针孔缺陷出现的原因及其对 C-TSV 应用产生的影响。研究证明,针孔缺陷 C-TSV 的缺陷空隙部分

会极大地加深 C-TSV 绝缘层与铜种子层之间的热分配失衡现象,呈现缺陷边缘应力集中现象,极端情况下可达  $1.2 \times 10^9 \, \text{N/m}^2$ ,为无缺陷 C-TSV 的 4 倍以上。并且随着升温载荷的施加,绝缘层缓解界面应力的能力将进一步下降,造成 C-TSV 界面出现裂纹、热循环寿命降低的隐患。最后,提出利用 C-TSV 深宽比等改变 C-TSV 结构的方法来对 C-TSV 进行针对性预防。本文的研究对于 C-TSV 的热应力分析及工业生产具有有效的参考价值,扩宽了 C-TSV 的检测与应用思路。

## 参考文献

- [1] 陈昊, 谢业磊, 庞健, 欧阳可青, 3D IC 系统架构概述[J]. 中兴通讯技术, 2024, 30(S1): 76-83.

- [2] 施建磊. 三维集成系统中硅通孔的制备工艺研究[D]: [硕士学位论文]. 贵阳: 贵州大学, 2021.

- [3] Wang, C., Huang, X. and Vafai, K. (2021) Analysis of Hotspots and Cooling Strategy for Multilayer Three-Dimensional Integrated Circuits. *Applied Thermal Engineering*, 186, Article ID: 116336. https://doi.org/10.1016/j.applthermaleng.2020.116336

- [4] 尚玉玲, 孙丽媛. TSV 互连结构缺陷故障测试[J]. 桂林电子科技大学学报, 2017, 37(5): 382-386.

- [5] Gerakis, V., Liolios, A. and Hatzopoulos, A. (2014) Modeling of Partially Cracked and Void Hole Defected through Silicon via Interconnections. *Design of Circuits and Integrated Systems*, Madrid, 26-28 November 2014, 1-6. <a href="https://doi.org/10.1109/dcis.2014.7154073">https://doi.org/10.1109/dcis.2014.7154073</a>

- [6] 杨陈,张立文,杨贺,黄慧霞,曹磊. 同轴硅通孔热应力诱导界面分层失效研究[D]: [硕士学位论文]. 洛阳:河南科技大学,2023.

- [7] 王兴君, 史凌峰. 新型同轴型混合碳纳米管填充的硅通孔[D]: [博士学位论文]. 西安: 陕西国防工业职业技术学院, 2015.

- [8] 谈豪. 基于碳纳米管的同轴型硅通孔电传输特性分析[D]: [硕士学位论文]. 西安: 西安电子科技大学, 2022.

- [9] 任嘉硕. 硅通孔热机械可靠性研究[D]: [硕士学位论文]. 西安: 西安理工大学, 2024.

- [10] 耿烨. 三维集成电路绑定前 TSV 缺陷检测方法研究[D]: [硕士学位论文]. 北京: 北京化工大学, 2016.