# 一种低功耗全MOS电压基准源

余璐洋<sup>1</sup>, 刘大伟<sup>2</sup>, 王志双<sup>1</sup>, 庄 魏<sup>2</sup>, 范建林<sup>2\*</sup>

<sup>1</sup>五邑大学电子与信息工程学院, 广东 江门

<sup>2</sup>广东省科学院半导体研究所, 广东 广州

收稿日期: 2025年2月21日; 录用日期: 2025年3月14日; 发布日期: 2025年3月21日

## 摘要

本文提出了一种低功耗全MOS电压基准源设计, 利用MOS管在亚阈值区的温度特性, 降低了功耗并满足低电压、宽温度范围的需求。传统的带隙基准源由于采用双极管和电阻, 无法满足低功耗应用的要求, 因此, 本文设计了一种全MOS管的基准电压源, 通过优化电路结构和工作原理, 实现了低静态功耗、较宽的工作温度范围和较低的温度系数。仿真结果显示, 在-55°C到150°C的温度范围内, 输出电压变化仅为2.03 mV, 温度系数为 $16.5 \times 10^{-6}/\text{°C}$ , 静态电流为5.7  $\mu\text{A}$ , 功耗为6.84  $\mu\text{W}$ , PSRR为-59.16 dB。该设计在低功耗、低电压应用中具有显著优势, 适用于物联网、可穿戴设备等对功耗要求较高的场合。

## 关键词

低功耗, MOS电压基准源, 亚阈值区, 低温度系数

# A Low-Power All-MOS Voltage Reference

Luyang Yu<sup>1</sup>, Dawei Liu<sup>2</sup>, Zhishuang Wang<sup>1</sup>, Wei Zhuang<sup>2</sup>, Jianlin Fan<sup>2\*</sup>

<sup>1</sup>School of Electronics and Information Engineering, Wuyi University, Jiangmen Guangdong

<sup>2</sup>Institute of Semiconductors, Guangdong Academy of Sciences, Guangzhou Guangdong

Received: Feb. 21<sup>st</sup>, 2025; accepted: Mar. 14<sup>th</sup>, 2025; published: Mar. 21<sup>st</sup>, 2025

## Abstract

This paper proposes a low-power all-MOS voltage reference design that utilizes the temperature characteristics of MOS transistors operating in the subthreshold region to achieve low power consumption while meeting the requirements of low voltage and wide temperature range. Traditional bandgap reference circuits, which rely on bipolar junction transistors and resistors, fail to satisfy the demands of low-power applications. Therefore, this design adopts an all-MOS voltage reference structure. By optimizing the circuit architecture and operational principles, the design achieves low

\*通讯作者。

**static power consumption, a wide operating temperature range, and a low temperature coefficient. Simulation results show that within the temperature range of  $-55^{\circ}\text{C}$  to  $150^{\circ}\text{C}$ , the output voltage variation is only 2.03 mV, with a temperature coefficient of  $16.5 \times 10^{-6}/^{\circ}\text{C}$ . The static current is 5.7  $\mu\text{A}$ , power consumption is 6.84  $\mu\text{W}$ , and the power supply rejection ratio (PSRR) is  $-59.16$  dB. This design demonstrates significant advantages in low-power, low-voltage applications, making it suitable for use in IoT devices, wearable electronics, and other scenarios with stringent power consumption requirements.**

## Keywords

**Low Power, MOS Voltage Reference, Subthreshold Region, Low Temperature Coefficient**

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

<http://creativecommons.org/licenses/by/4.0/>

Open Access

## 1. 引言

低电压、低功耗基准电压源具有广阔的应用前景。物联网是近年来发展最快的领域之一，其中大量设备需要长时间运行，例如传感器、智能家居等[1]。低电压、低功耗基准电压源能够为这些设备提供长时间稳定的输出电压参考源，从而保证设备的正常运行。可穿戴设备也随着互联网的发展而不断普及，其需要采用超低功耗芯片，以延长电池寿命，同时保证设备的可用性。低电压、低功耗基准电压源作为芯片中最基本的模块之一，可以在保证设备长时间运行的同时，节约能源。

然而，传统的带隙基准源是根据双极型晶体管的  $V_{BE}$  和  $\Delta V_{BE}$  的温度特性来设计的，在 CMOS 工艺中采用了寄生的 PNP 管进行设计，其带隙基准电压为：

$$V_{ref} \Big|_{T=T_0} = V_{G0} + V_{T0}(\gamma - \alpha) \quad (1)$$

其中， $V_{ref}$  是温度为  $T_0$  时的基准电压， $V_{G0}$  是带隙电压(1.205 V)，对于典型值  $\gamma = 3.2$ ， $\alpha = 1$ ， $V_{ref} = 1.262$  V [2]。一般带隙基准电路其基准电压都大于带隙电压，难以实现低压，已经逐渐无法满足设计要求。本文设计了一种新颖的全 MOS 管基准源电路结构，通过 MOS 管的亚阈值温度特性实现低电源电压宽温度范围的基准源。

## 2. 传统的 CMOS 带隙基准源

传统的带隙基准电压源由 CMOS 运算放大器、电阻和二极管连接的双极晶体管组成。

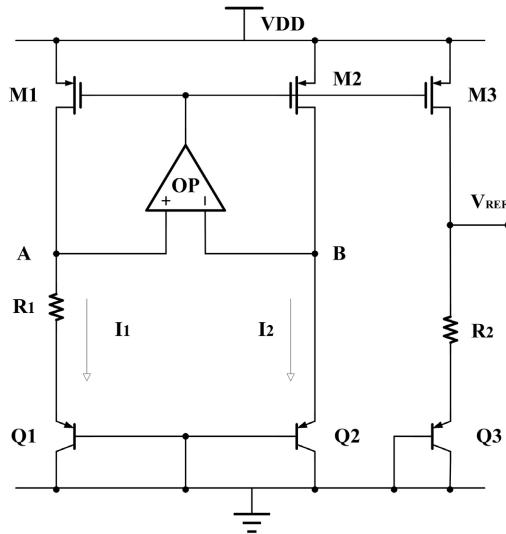

如图 1 为传统的 CMOS 带隙基准源，PMOS 管 M1、M2、M3 的尺寸完全相同，双极晶体管 Q1 的发射极面积是 Q2 的  $N$  倍。通过负反馈，运放钳位 A 节点和 B 节点电压，使  $V_A$  等于  $V_B$ 。晶体管 Q1、Q2、R1 组合产生具有正温度系数的电流  $I_1$ ，通过电流镜 M1、M2、M3 镜像电流  $I_1$ ，在电阻 R2 上产生压降与  $V_{BE3}$  相加获得基准电压  $V_{REF}$  [3]。

传统的带隙基准电路是使用电阻之间的比例来控制输出基准电压的温度系数以及使用电阻来控制每一路电路的电流大小[4]，但是在低功耗的基准源中却不能使用电阻。当电路中的电流为纳安级别时，那需要使用兆欧级别的电阻，所用电阻占有很大的版图面积，并且传统的带隙基准产生的基准电压在 1.2 V 左右，不能满足低电压的需求[5]。

为了达到低功耗的目标，需要让 MOS 管的工作电流为纳安级别，MOS 管需工作在亚阈值区，其工

作电流是纳安级别。本文将基于 MOS 管亚阈值区工作特性设计低功耗基准电压源。

**Figure 1.** Traditional CMOS bandgap reference circuit

**图 1.** 传统 CMOS 带隙基准电路

### 3. 亚阈值 CMOS 基准源原理

对于 MOSFET 的电流电压特性，当栅源电压小于或等于阈值电压时，MOS 晶体管不会完全关断，此时仍然存在较小的漏电流，这时的漏电流是由于器件的源极和漏极的载流子浓度不相同而产生的扩散电流[6]。这种工作区下的 MOS 器件的电学特性和 BJT 双极管的电学特性相似，此时的源漏电流与栅源电压  $V_{GS}$  呈现指数关系，MOSFET 的这种导电称为亚阈值导电，这个工作区域称为亚阈值区域[7]。亚阈值电流  $I_{D_{SUB}}$  大小与栅极电压以及漏源极电压的关系可以由以下公式表示：

$$I_{D_{SUB}} = \mu C_{OX} V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{mV_T}\right) \left[1 - \exp\left(-\frac{V_{DS}}{V_T}\right)\right] \quad (2)$$

因为  $V_{DS}$  远远大于  $V_T$ ，所以  $1 - \exp\left(-\frac{V_{DS}}{V_T}\right)$  可以约等于 1。

所以 MOS 管处于亚阈值状态的漏电流公式为：

$$I_{D_{SUB}} = \mu C_{OX} V_T^2 \exp\left(\frac{V_{GS} - V_{TH}}{mV_T}\right) \quad (3)$$

从而可以得出亚阈值 MOS 管的栅源电压公式为：

$$V_{GS} = mV_T \ln \left( \frac{I_{D_{SUB}}}{\mu C_{ox} V_T^2 \left( \frac{W}{L} \right)} \right) + V_{TH} \quad (4)$$

#### 4. 亚阈值基准电压源电路设计

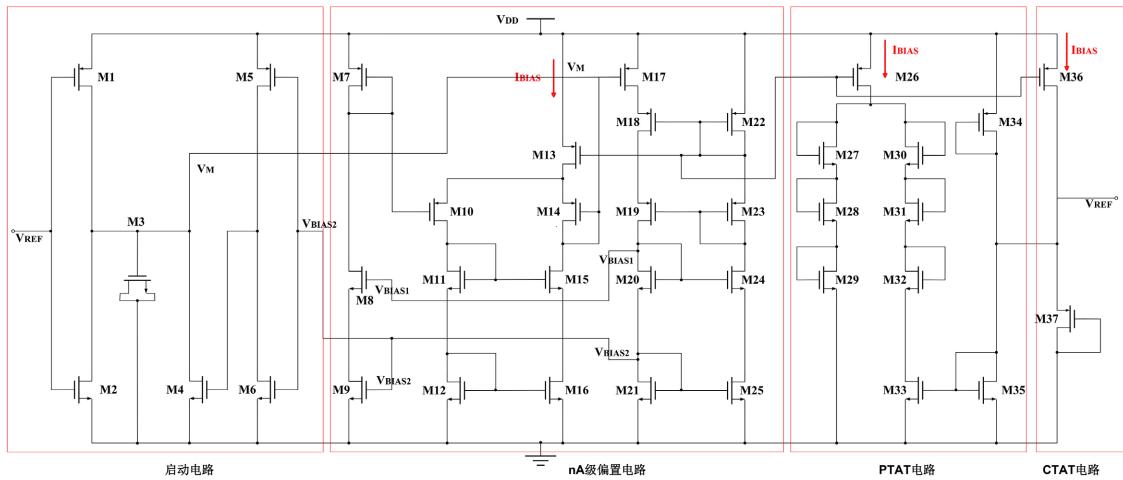

本文基准电压源电路整体电路如图2所示，整个基准电路分为四个部分，启动电路、nA级电流生成偏置电路、正温度系数电压产生电路和负温度系数电压产生电路。

Figure 2. Overall circuit of the proposed reference circuit

图2. 本文基准电路总体电路

#### 4.1. 启动电路

初始状态,  $V_{REF}$  处于低电平状态, 使得 PMOS 管  $M_1$  导通, 电压源  $V_{DD}$  给 MOS 电容  $M_3$  充电将节点电压拉高, 此时通过  $V_M$  节点向偏置电路中的  $M_{17}$  管注入电流并使偏置电路中的 MOS 管工作在亚阈值区, 此刻  $V_{BIAS2}$  是高电位,  $M_6$  管导通将电压拉低使得  $M_4$  管不工作。当偏置电流产生电路稳定导通后,  $V_{BIAS2}$  是低电位,  $M_5$  管导通将节点电压拉高使得  $M_4$  管漏极电压拉低, MOS 电容  $M_3$  放电,  $V_M$  节点停止向偏置电路的电流注入, 完成启动并关闭启动电路。

#### 4.2. nA 级偏置电路

偏置电流产生电路分为  $M_{17}$  栅压控制电路和偏置电流产生电路。通过控制  $M_{10}$  和  $M_{14}$  的面积之比来控制偏置电流的大小,  $M_{13}$  为  $M_{10}$  和  $M_{14}$  提供偏置电流,  $M_8$  和  $M_9$  为  $M_7$  提供偏置。此偏置电路产生的偏置电流  $I_{BIAS}$  公式为:

$$I_{BIAS} = \mu_p C_{OX} \left( \frac{W}{L} \right)_{M17} \left( \frac{nKT}{q} \right)^2 \ln 3 \ln \left[ \frac{5I_{M17}}{2n\mu_p C_{OX} \left( \frac{W}{L} \right)_{M17} \left( \frac{KT}{q} \right)^2} \right] \quad (5)$$

式中  $\mu_p$  为半导体中空穴迁移率,  $\left( \frac{W}{L} \right)_{M17}$  为 MOS 管  $M_{17}$  的宽长比为 1:5, 生成约 10 nA 的偏置电流为 PTAT 电路提供偏置。

#### 4.3. PTAT 产生电路

正温度系数电压产生电路通过偏置电路产生的 nA 级偏置电流, 使得  $M_{27} \sim M_{32}$  管均处于亚阈值区。

由  $M_{27}$ 、 $M_{28}$ 、 $M_{29}$  构成的支路栅源电压记为  $V_{GS1}$ , 由  $M_{30}$ 、 $M_{31}$ 、 $M_{32}$  构成的支路栅源电压记为  $V_{GS2}$ 。

$$V_{GS1} = mV_T \ln \left( \frac{I_{M27} \times I_{M28} \times I_{M29}}{\left( \mu C_{OX} V_T^2 \right)^3 \left( \frac{W}{L} \right)_{M27} \left( \frac{W}{L} \right)_{M28} \left( \frac{W}{L} \right)_{M29}} \right) + 3V_{TH} \quad (6)$$

$$V_{GS2} = mV_T \ln \left( \frac{I_{M30} \times I_{M31} \times I_{M32}}{\left( \alpha \mu C_{ox} V_T^2 \right)^3 \left( \frac{W}{L} \right)_{M30} \left( \frac{W}{L} \right)_{M31} \left( \frac{W}{L} \right)_{M32}} \right) + 3V_{TH} \quad (7)$$

$$\Delta V_{GS} = V_{GS1} - V_{GS2} = mV_T \ln \left( \alpha^3 \frac{I_{M27} \times I_{M28} \times I_{M29}}{I_{M30} \times I_{M31} \times I_{M32}} \right) \quad (8)$$

$\alpha$  为支路  $V_{GS1}$  与  $V_{GS2}$  中 MOS 管的宽长比,  $V_T$  与温度成正相关, 随着温度增加,  $V_T$  增大, 所以可以通过调整  $\alpha$  的值获得相应的正温度系数电压。

$M_{33}$  为工作在深线性区的 MOS 管, 漏源电流公式为:

$$I_{M33} = \mu C_{ox} \left( \frac{W}{L} \right)_{M33} (V_{GS} - V_{TH}) V_{DS} \quad (9)$$

$M_{35}$  为工作在饱和区的 MOS 管, 其漏源电流公式为:

$$I_{M35} = \frac{1}{2} \mu C_{ox} \left( \frac{W}{L} \right)_{M35} (V_{GS} - V_{TH})^2 \quad (10)$$

因为  $M_{33}$  和  $M_{35}$  的栅源电压相等, 宽长比相等, 所以  $I_{M33} = \beta I_{M35}$ ,  $\beta$  为 MOS 管  $M_{33}$  与  $M_{35}$  宽长比。所以可得  $M_{35}$  的漏源电流为:

$$I_{M35} = 2\beta^2 \mu C_{ox} \left( \frac{W}{L} \right)_{M35} V_{DS}^2 \quad (11)$$

由于  $M_{33}$  的漏源电压为:

$$V_{DS} = \Delta V_{GS} = mV_T \ln \left( \alpha^3 \frac{I_{M27} \times I_{M28} \times I_{M29}}{I_{M30} \times I_{M31} \times I_{M32}} \right) \quad (12)$$

$$I_{M35} = 2\beta^2 \mu C_{ox} \left( \frac{W}{L} \right)_{M35} m \ln \left( \alpha^3 \frac{I_{M27} \times I_{M28} \times I_{M29}}{I_{M30} \times I_{M31} \times I_{M32}} \right) V_T^2 \quad (13)$$

$$V_{GS_{M35}} = V_{TH} + 2\beta \sqrt{\ln \left( \alpha^3 \frac{I_{M27} \times I_{M28} \times I_{M29}}{I_{M30} \times I_{M31} \times I_{M32}} \right) V_T} \quad (14)$$

#### 4.4. CTAT 产生电路

$M_{37}$  为工作在饱和区的 PMOS 管, 其电流公式为:

$$I_{M37} = \frac{1}{2} \mu C_{ox} \left( \frac{W}{L} \right)_{M37} (V_{GS} - V_{TH})^2 \quad (15)$$

由此可得栅源电压为:

$$V_{GS_{M37}} = V_{TH} + \sqrt{\frac{2I}{\mu C_{ox} \left( \frac{W}{L} \right)_{M37}}} \quad (16)$$

$V_{TH}$  与温度成负相关, 随着温度的增大而减小。

$$V_{REF} = 2V_{TH} + 2\beta \sqrt{\ln \left( \alpha^3 \frac{I_{M27} \times I_{M28} \times I_{M29}}{I_{M30} \times I_{M31} \times I_{M32}} \right) V_T} + \sqrt{\frac{2I}{\mu C_{ox} \left( \frac{W}{L} \right)_{M37}}} \quad (17)$$

所以可以通过调节  $\alpha$ 、 $\beta$  的值和  $M_{37}$  管的宽长比, 来获得一个与温度无关的基准电压源, 并且有较宽的温度范围和较低的功耗, 同时本发明采用的全 MOS 结构能够有效地减小版图面积。

## 5. 电路仿真与分析

**Table 1.** Key device parameters of the proposed reference circuit

**表 1.** 本文基准电路核心器件参数

| 器件                             | 参数            | 器件       | 参数           |

|--------------------------------|---------------|----------|--------------|

| $M_{26}$                       | $W/L = 3:3$   | $M_{35}$ | $W/L = 1:10$ |

| $M_{27}$ 、 $M_{28}$ 、 $M_{29}$ | $W/L = 1:10$  | $M_{34}$ | $W/L = 10:1$ |

| $M_{30}$ 、 $M_{31}$ 、 $M_{32}$ | $W/L = 15:10$ | $M_{36}$ | $W/L = 3:3$  |

| $M_{33}$                       | $W/L = 1:10$  | $M_{37}$ | $W/L = 36:6$ |

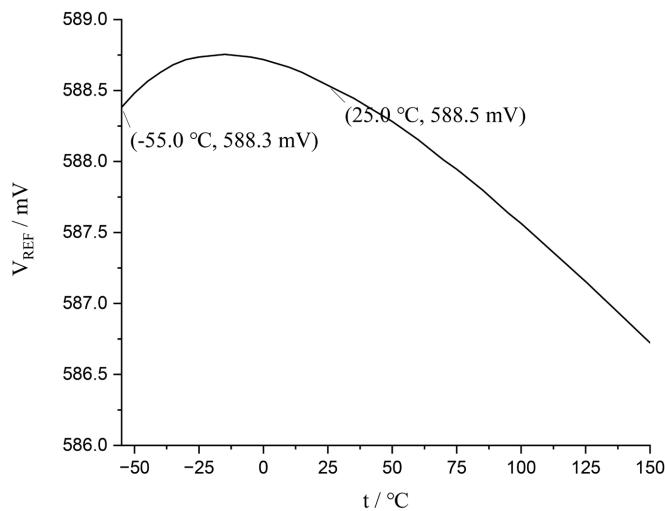

**Figure 3.** Temperature characteristics of the reference output voltage

**图 3.** 基准输出电压温度特性曲线

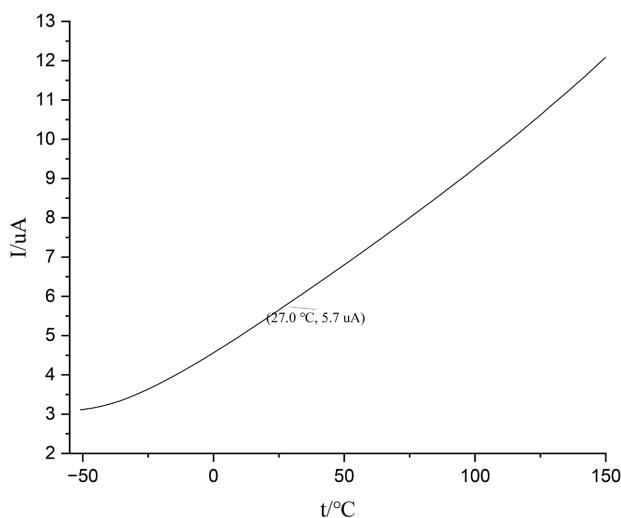

**Figure 4.** Temperature characteristics of the quiescent current of the reference circuit

**图 4.** 基准静态电流温度特性曲线

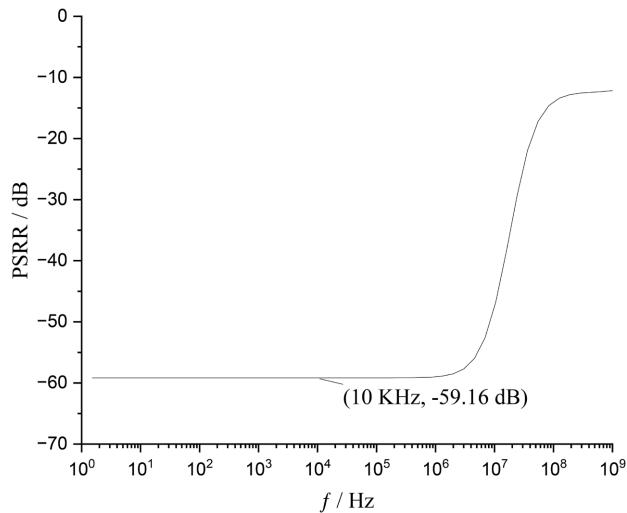

**Figure 5.** Power supply rejection ratio curve of the reference circuit at room temperature

**图 5.** 室温下基准电源抑制比曲线

电路基于  $0.18\text{ }\mu\text{m}$  CMOS 工艺, 使用 cadence 软件在典型工艺角下对电路进行了仿真分析。表 1 为基准电路中 PTAT 产生电路和 CTAT 产生电路器件参数。

当电源电压为  $1.2\text{ V}$ , 温度范围为  $-55\text{ }^{\circ}\text{C} \sim +150\text{ }^{\circ}\text{C}$  时, 输出电压温度特性仿真结果如图 3 所示。从图 1 中可以看出, 在  $-55\text{ }^{\circ}\text{C} \sim +150\text{ }^{\circ}\text{C}$  温度范围内, 电压变化  $2.03\text{ mV}$ , PPM (温度系数) 为  $16.5 \times 10^{-6}/\text{ }^{\circ}\text{C}$ 。

从图 4 静态电流温度曲线可以看出,  $27\text{ }^{\circ}\text{C}$  时静态电流为  $5.7\text{ }\mu\text{A}$ , 因此, 电路总静态功耗为  $6.84\text{ }\mu\text{W}$ 。

图 5 的仿真结果显示室温下基准在  $10\text{ kHz}$  时的 PSRR (电源抑制比) 为  $-59.16\text{ dB}$ 。

**Table 2.** Comparison of voltage reference performance metrics between this work and other literature

**表 2.** 本文与其他文献的电压基准性能指标对比

| 参数                                                                       | 文献 1           | 文献 2            | 文献 3            | 文献 4            | 本文              |

|--------------------------------------------------------------------------|----------------|-----------------|-----------------|-----------------|-----------------|

| 工艺/ $\mu\text{m}$                                                        | 0.18           | 0.18            | 0.35            | 0.18            | 0.18            |

| 电源电压/V                                                                   | 3              | 1.8             | 1.8             | 1.8             | 1.2             |

| 输出电压/mV                                                                  | 591.6          | 992             | 597             | 993             | 588             |

| 温度范围/ $^{\circ}\text{C}$                                                 | $-20 \sim +80$ | $-50 \sim +150$ | $-50 \sim +100$ | $-55 \sim +125$ | $-55 \sim +150$ |

| 温度系数/ $(10\text{ }^{\circ}\text{C} \sim 6\text{ }^{\circ}\text{C}^{-1})$ | 25             | 22.6            | 39              | 17.49           | 16.5            |

| 静态电流/ $\mu\text{A}$                                                      | 0.53           | 0.33            | 0.12            | 4.416           | 5.7             |

| PSRR/dB                                                                  |                | -26.3           | -64             | -56.05          | -59.16          |

表 2 列出了本文与其他文献的电路参数的对比, 可以看出, 与文献[1]-[4]相比, 本文设计的电路温度范围更广, 温度系数更低。并且电路的电源电压更低, 因此更适合于供电电压较低的场合。

## 6. 结论

本文通过对 MOS 晶体管在亚阈值区、线性区和饱和区的不同电流特性的分析提出了一种低功耗全 MOS 电压基准源, 利用亚阈值区 MOS 管特性降低了基准电路的整体功耗, 并利用线性区 MOS 管代替常规电阻降低了芯片面积。仿真结果显示: 在  $-55 \sim +150\text{ }^{\circ}\text{C}$  温度范围内, 温度系数为  $16.5 \times 10^{-6}/\text{ }^{\circ}\text{C}$ , 基准

电压源电路输出电压约为 588 mV, 27°C 时静态电流为 5.7 μA, 整个电路功耗为 6.84 μW, 10 kHz 处的电源抑制比为 -59.16 dB。

## 基金项目

本工作受到广东省科学院半导体研究所的资助, 资助项目编号为 2020GDASYL-20200102025、2021GDASYL-20210102001 和 2022GDASZH-2022010203。

## 参考文献

- [1] Zhang, J., Luo, Y., Wang, Q., Li, J., Gong, Z., Tan, H., *et al.* (2012) A Low-Voltage, Low-Power Subthreshold CMOS Voltage Reference without Resistors and High Threshold Voltage Devices. *2012 IEEE Asia Pacific Conference on Circuits and Systems*, Kaohsiung, 2-5 December 2012, 384-387. <https://doi.org/10.1109/apccas.2012.6419052>

- [2] 张涛, 陈远龙, 王影, 等. 一种低功耗亚阈值全 MOS 管基准电压源的设计[J]. 电子元件与材料, 2016, 35(5): 27-30.

- [3] 仲召扬, 李严. 低功耗高性能的全 MOS 电压基准源设计[J]. 微处理机, 2020, 41(3): 1-4.

- [4] 田伟娜. 宽温度全 MOS 电压基准源电路设计[D]: [硕士学位论文]. 南京: 东南大学, 2017.

- [5] Zhang, H., Li, D., Wang, Q., *et al.* (2014) A Resistor-Less Bandgap Reference with Improved PTAT Generator for Ultra-Low-Power LSIs. *2014 IEEE Faible Tension Faible Consommation*, Monaco, 4-6 May 2014, 1-4. <https://doi.org/10.1109/ftfc.2014.6828605>

- [6] Razavi, B. 模拟 CMOS 集成电路设计[M]. 陈贵灿, 程军, 译. 西安: 西安交通大学出版社, 2003: 23-24.

- [7] Allen, P. and Holberg, D.R. CMOS 模拟集成电路设计[M]. 冯军, 李智群, 译. 北京: 电子工业出版社, 2002: 78-80.