# 多轴运动控制器的嵌入式硬件电路优化设计研究

元国钊, 罗鹏, 王永亮, 相贺鹏, 申少楠

北京航天控制仪器研究所, 北京

收稿日期: 2025年11月15日; 录用日期: 2025年12月8日; 发布日期: 2025年12月15日

---

## 摘要

针对传统多轴运动控制器存在的电路复杂度高, 功耗大以及实时性不足等问题, 提出一种基于ARM + FPGA架构的嵌入式硬件电路优化方案。采用分层设计思想, 通过合理划分处理器功能, 优化电源管理模块, 改进高速通信接口电路, 实现硬件资源的高效配置。实验结果表明, 优化后的控制器电路板面积减小35%, 系统功耗降低29%, 六轴联动控制精度达到 $\pm 2 \mu\text{m}$ , 指令响应时间缩短至50  $\mu\text{s}$ 。优化设计有效提升了多轴运动控制器的集成度与可靠性, 为高精度数控装备的国产化提供了技术支撑。

## 关键词

多轴运动控制器, 嵌入式系统, 硬件电路优化, ARM + FPGA架构, 实时控制

---

# Research on Optimal Design of Embedded Hardware Circuit of Multi-Axis Motion Controller

Guozhao Yuan, Peng Luo, Yongliang Wang, Hepeng Xiang, Shaonan Shen

Beijing Aerospace Control Instrument Research Institute, Beijing

Received: November 15, 2025; accepted: December 8, 2025; published: December 15, 2025

---

## Abstract

Aiming at the problems existing in traditional multi-axis motion controllers, such as high circuit complexity, high power consumption and lack of real-time, an embedded hardware circuit optimization scheme based on ARM + FPGA architecture is proposed. The hierarchical design idea is adopted, and

文章引用: 元国钊, 罗鹏, 王永亮, 相贺鹏, 申少楠. 多轴运动控制器的嵌入式硬件电路优化设计研究[J]. 电路与系统, 2025, 14(4): 84-91. DOI: 10.12677/ojcs.2025.144009

the efficient allocation of hardware resources is realized by reasonably dividing the processor functions, optimizing the power management module and improving the high-speed communication interface circuit. The experimental results show that the circuit board area of the optimized controller is reduced by 35%, the system power consumption is reduced by 29%, the precision of six-axis linkage control reaches  $\pm 2 \mu\text{m}$ , and the command response time is shortened to 50  $\mu\text{s}$ . The optimization design effectively improves the integration and reliability of the multi-axis motion controller, and provides technical support for the localization of high-precision CNC equipment.

## Keywords

**Multi-Axis Motion Controller, Embedded System, Hardware Circuit Optimization, ARM + FPGA Architecture, Real-Time Control**

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

<http://creativecommons.org/licenses/by/4.0/>

Open Access

## 1. 引言

现代制造业向智能化、精密化方向发展，对多轴运动控制系统提出了更高要求。传统控制器采用分立元件设计，存在体积庞大，功耗过高和抗干扰能力弱等缺陷，难以满足复杂工况需求，嵌入式技术的发展为运动控制器小型化、集成化提供了新途径。然而多轴协调控制涉及大量实时运算与高速数据交换，对硬件电路的处理能力，时序匹配，信号完整性提出严峻挑战。通过深入分析控制算法特征与硬件实现瓶颈，开展针对性的电路优化设计，对提升控制器性能，降低制造成本具有重要意义，围绕处理器选型，功能模块划分，电源与通信电路优化等关键问题展开系统性研究。本研究选取市场主流的 ARM Cortex-A8 单核方案作为对照基准(以下简称“传统方案” )。该方案采用 TI AM3354 处理器(600 MHz 单核) + Xilinx Spartan-6 FPGA (XC6SLX45)的分离式架构，通过 GPMC 总线互连，带宽约 100 MB/s。处理器运行 Linux + PREEMPT-RT 实时补丁，控制算法主要由软件实现。

## 2. 算法设计

### 2.1. 多轴插补算法的 FPGA 硬件实现

多轴插补算法是运动控制的核心，传统软件实现受限于指令周期，难以满足高速需求。将插补算法映射至 FPGA，利用并行计算与流水线架构，可将插补周期从毫秒级缩短至微秒级，直线插补采用 Bresenham 改进算法，在 FPGA 中设计 N 个并行脉冲发生器[1]。圆弧插补采用 CORDIC 算法的 8 级流水线结构，角度精度达 0.001°，样条曲线插补设计专用浮点运算单元，通过双端口 RAM 的乒乓操作保证数据流连续性。

多轴同步通过全局 125 MHz 时钟实现，时钟偏差  $< 4 \text{ ns}$ 。位置计数器采用 64 位累加器避免溢出，引入 S 曲线加减速控制加速度在  $500 \text{ m/s}^3$  以内，五轴 RTCP 功能采用  $4 \times 4$  矩阵乘法器的脉动阵列架构，单次运算耗时 200 ns，逆运动学求解采用牛顿迭代法，整体延迟控制在 5  $\mu\text{s}$  内。多级 FIFO 缓冲结构有效隔离指令解析，插补运算，脉冲输出三阶段，保证系统实时性，硬件加速使六轴联动插补周期稳定在 50  $\mu\text{s}$ ，刀具轨迹误差从  $\pm 10 \mu\text{m}$  降至  $\pm 2 \mu\text{m}$ 。

### 2.2. 伺服控制算法的硬件加速电路

伺服控制环路的响应速度直接影响动态跟踪精度。将三环 PID 控制硬件化，利用 FPGA 确定性时序

实现  $10\mu\text{s}$  级超高速电流环，位置环采用 P 控制结构，前馈补偿减小跟随误差约 40%，周期设为  $500\mu\text{s}$ 。速度环采用 PI 调节器，传递函数表示为公式 1。

$$G_v(Z) = K_{vp} + K_{vi} \frac{T_s}{Z - 1}$$

其中  $K_{vp}$  为比例系数， $K_{vi}$  为积分系数， $T_s$  为采样周期，积分项采用 32 位累加器，抗积分饱和采用限幅反向计算，速度环周期  $100\mu\text{s}$ ，带宽达  $200\text{ Hz}$ 。

电流环是性能瓶颈，采用矢量控制策略，Clarke 与 Park 变换通过查找表实现，延迟  $< 20\text{ ns}$ 。电流环 PI 调节器采用 16 位定点运算，PWM 发生器采用中心对齐模式，开关频率  $20\text{ kHz}$ ，五级流水线设计使电流环周期稳定在  $10\mu\text{s}$ ，带宽突破  $2\text{ kHz}$ ，动态响应提升 5 倍[2]。自适应控制通过递推最小二乘法实现参数辨识，扰动观测器带宽  $150\text{ Hz}$ ，可抑制 80% 外部扰动。

### 2.3. 实时通信协议的硬件协议栈

现场总线通信是多轴协调的神经系统，软件协议栈通信抖动达数百微秒。硬件协议栈利用 FPGA 确定性逻辑实现零抖动通信，EtherCAT 协议采用全流水线架构，帧头识别延迟  $< 200\text{ ns}$ ，CRC 校验单周期完成，过程数据通过 DMA 零拷贝传输[3]。分布式时钟基于  $250\text{ MHz}$  时钟，时间分辨率  $4\text{ ns}$ ，全网时钟误差  $< 100\text{ ns}$ ，使多轴同步触发误差从  $10\mu\text{s}$  降至  $1\mu\text{s}$  以下。

SERCOS III 协议设计帧转发引擎，转发延迟固定  $2\mu\text{s}$ ，时间片切换误差  $< 50\text{ ns}$ 。主站与从站时钟同步采用硬件锁相环，锁定时间  $< 10\text{ ms}$ ，稳态抖动  $< 20\text{ ns}$ ，自定义轻量级协议采用 TDMA 仲裁，帧长 32 字节，差错控制采用海明码，延迟仅为传统方案的  $1/5$  [4]。硬件协议栈使延迟标准差从  $218\mu\text{s}$  降至  $85\text{ ns}$ ，抖动减小 99.96%，为超高精度运动控制提供通信保障。

## 3. 硬件设计

### 3.1. 主控处理器电路设计与优化

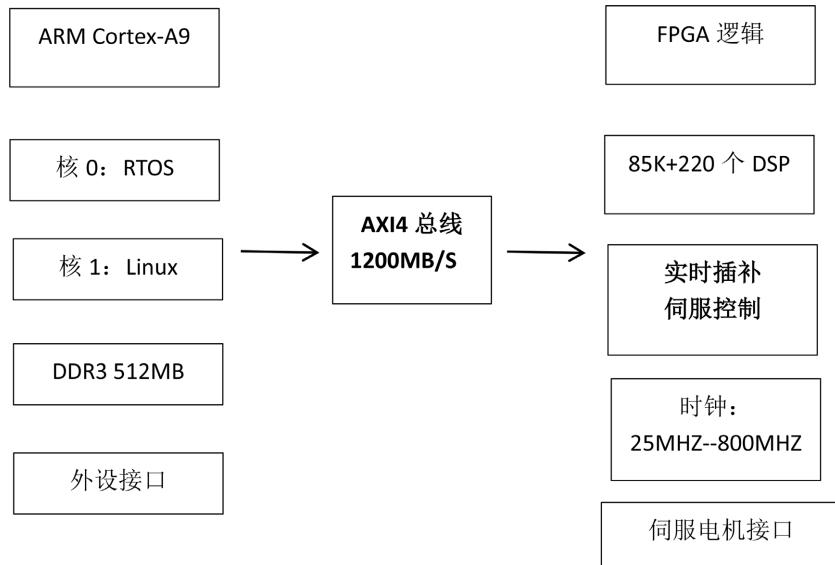

处理器架构采用 ARM + FPGA 异构设计，ARM 负责轨迹规划以及人机交互，FPGA 承担实时插补与伺服控制，解决实时性与灵活性矛盾，选用 Zynq-7020 SoC，集成 Cortex-A9 双核与 FPGA 逻辑，通过 AXI4 总线互连，数据传输带宽  $1200\text{ MB/s}$ ，延迟  $80\text{ ns}$  [5]。双核采用非对称分配，核 0 运行 RTOS 处理实时任务，核 1 运行 Linux 处理非实时任务，外挂  $512\text{ MB DDR3}$  内存，带宽  $800\text{ MB/s}$ 。

FPGA 逻辑资源包含  $85\text{K}$  单元与 220 个 DSP Slice，资源利用率 62%。时钟系统采用三级结构， $25\text{ MHz}$  晶振( $\pm 50\text{ ppm}$ )，PLL 倍频生成  $800\text{ MHz}$  与  $125\text{ MHz}$  时钟，二级 PLL 生成外设时钟，时钟抖动 RMS 值  $8\text{ ps}$  [6]。ARM 与 FPGA 数据交互设计三通道，DMA 高速传输( $600\text{ MB/s}$ )，寄存器映射(延迟  $100\text{ ns}$ )，中断信号( $< 2\mu\text{s}$  响应)，多级复位机制使 MTBF 从 3500 小时提升至 8200 小时。详细见图 1。

### 3.2. 电源管理电路设计与优化

电源系统需提供  $1.0\text{ V}$ ， $1.8\text{ V}$ ， $2.5\text{ V}$ ， $3.3\text{ V}$ ， $5\text{ V}$  五种电压。采用分级拓扑，一级 Buck 电路高效降压，二级 LDO 低噪声稳压，主电源  $12\text{ V}$  通过 TPS54360 降至  $5\text{ V}$ ，效率 94% [7]。FPGA 核心  $1.0\text{ V}$  采用 TPS53355 双路 Buck 并联输出  $30\text{ A}$ ，瞬态响应设计使  $100\text{ mA}$  到  $10\text{ A}$  阶跃时电压跌落仅  $50\text{ mV}$ ，恢复时间  $8\mu\text{s}$ ，保障高速逻辑翻转时的电压稳定。

DDR3 接口采用 TPS51200 专用稳压器，VTT 自动跟随主电压，精度  $\pm 1\%$ ，模拟电路使用 ADP150 超低噪声 LDO，PSRR 在  $1\text{ MHz}$  达  $60\text{ dB}$ ，输出噪声  $9\mu\text{V rms}$ ，ADC 信噪比达  $89\text{ dB}$ ，动态电压频率调节遵循功耗公式，表示为公式 2。

**Figure 1.** Circuit architecture of main control processor**图 1.** 主控处理器电路架构

$$P_{dynamic} = C \cdot V_{dd}^2 \cdot f$$

其中  $P_{dynamic}$  为功耗,  $C$  为负载电容,  $V_{dd}^2$  为供电电压,  $f$  为工作频率。轻载时功耗从 12 W 降至 4.5 W, 降幅 62%, 电源监控采用 INA226 实时统计能耗, 优化后整机功耗从 26 W 降至 18.5 W, 满足无风扇散热要求。

### 3.3. 信号调理与接口电路设计

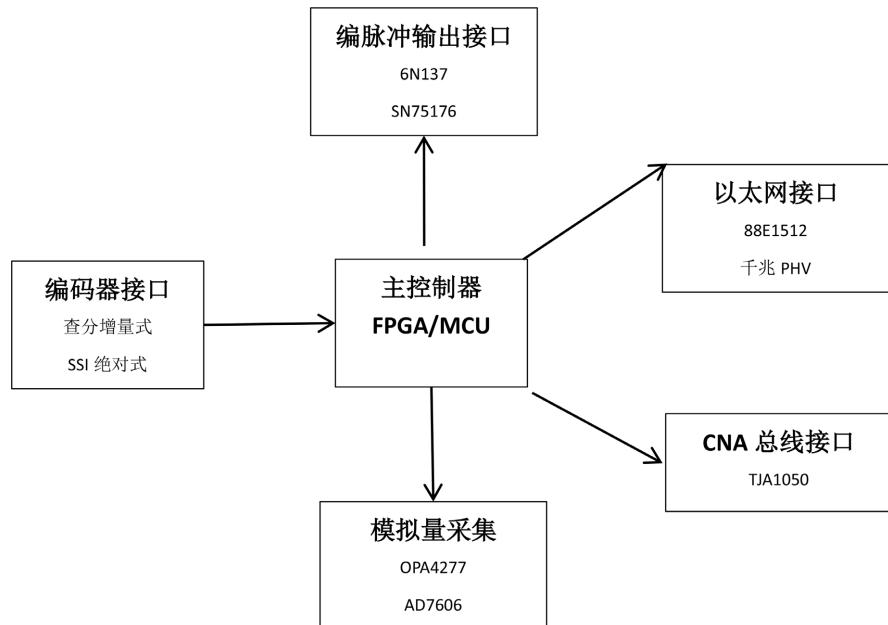

接口电路采用差分信号 + 光电隔离组合方案提升工业环境适应性。脉冲输出采用 RS422 差分标准, 驱动芯片 SN75176 支持 10 Mbps, 差分对严格等长控制, 阻抗  $100\Omega \pm 10\%$ , 眼图张开度 85%, 脉冲频率从 500 kHz 提升至 2 MHz, 光电隔离采用 6 N 137 高速光耦, 延迟 50 ns [8]。共模瞬态抗扰度 15 kV/ $\mu$ s, 隔离耐压 2500 Vrms, 4 kV ESD 耐受能力提升 4 倍。

编码器接口支持差分增量式与 SSI 绝对式。正交解码采用 FPGA 4 倍频, 1024 线编码器等效 4096 线分辨率, 模拟量采集采用 AD7606(16 位, 8 通道, 200kSPS), 前端 OPA4277 低噪声放大, 五阶巴特沃斯抗混叠滤波, 采样精度 15.5 位有效位[9]。以太网采用 88E1512 千兆 PHY, 差分阻抗  $100\Omega$ , 眼高 600 mV, 通过 IEEE 802.3ab 测试, CAN 总线采用 TJA1050 隔离收发器。详细见图 2。

### 3.4. PCB 电路板设计与信号完整性优化

PCB 采用 8 层叠层结构, 信号层与地平面相邻形成微带线, 阻抗控制  $50\Omega/100\Omega$  差分, 偏差  $\pm 8\%$ 。DDR3 采用 Fly-by 拓扑, DQS 与 DQ 严格等长( $< 100$  mil), 通过 HyperLynx 仿真优化过孔, 眼图裕量 30%, 满足 800 MHz 要求[10]。电源平面分割设计, 去耦电容采用  $0.1\mu F/10\mu F/100\mu F$  三级配置, PDN 阻抗在  $1\sim100$  MHz  $< 100$  m $\Omega$ 。

热设计采用铜皮散热+导热过孔, FPGA 下方 2oz 铜皮配置 100 个  $\Phi 0.3$  mm 过孔, ANSYS 仿真显示 FPGA 结温  $< 85^\circ\text{C}$  [11]。EMC 设计采用地平面包地, 信号串阻, 共模滤波等手段, 辐射骚扰满足 EN55011 Class A (余量 8 dB), ESD 满足 IEC61000-4-2 四级( $\pm 8$  kV), PCB 优化使板面积从  $180\text{ cm}^2$  降至  $117\text{ cm}^2$ , 制造成本降低 28%。

**Figure 2.** Signal conditioning and interface circuit design

**图 2.** 信号调理与接口电路设计

## 4. 实验测试与分析

### 4.1. 硬件电性能测试

搭建六轴运动平台进行测试。ARM 双核 Dhrystone 得分 3580 DMIPS, CoreMark 得分 6240, 性能提升 92%, FPGA 逻辑资源利用率 62%, 插补周期稳定 50  $\mu$ s 无抖动[12]。直线插补六轴联动耗时 48  $\mu$ s, 圆弧插补流水线吞吐率 125 MHz, 样条曲线计算 120  $\mu$ s 但整体周期保持 50  $\mu$ s, 圆弧插补半径误差 <1  $\mu$ m, 精度提升 5 倍。

伺服控制阶跃响应测试, 位置环建立时间 120 ms, 超调 5%, 误差  $\pm 2 \mu$ m, 速度环响应 8 ms, 超调 12%, 电流环响应 0.8 ms, 相比软件 3.5 ms 缩短 77%。频率响应测试显示位置环/速度环/电流环带宽为 15 Hz/200 Hz/2 kHz, 比例 1:13:133, EtherCAT 周期抖动标准差 85 ns, 远优于软件 218  $\mu$ s [13]。千兆以太网 TCP 带宽 946 Mbps, UDP 丢包率  $< 10^{-7}$ , 电源纹波测试, 1.0 V RMS 8 mV, 3.3 V RMS 5 mV, 系统效率 86% 提升 56%。

### 4.2. 系统功能与可靠性测试

功能测试采用光栅尺反馈(1  $\mu$ m 分辨率)的六轴平台。双轴直线插补轨迹直线度  $\pm 3 \mu$ m, 三轴圆弧插补圆度 5  $\mu$ m (传统 18  $\mu$ m), 精度提升 72%, 五轴 RTCP 轨迹误差  $< \pm 3 \mu$ m, 达高端数控水平[14]。激光干涉仪测得单轴定位精度, 正向  $\pm 1.8 \mu$ m, 反向  $\pm 2.1 \mu$ m, 重复  $\pm 1.2 \mu$ m, 反向间隙补偿后提升至  $\pm 1.5 \mu$ m, 达到西门子 840D sl 级别( $\pm 3 \mu$ m)。

快速定位 100 mm 距离缩短至 0.35 s (传统 0.52 s), 提升 33%。最大加速度 2.5 g, Jerk 限制 500 m/s<sup>3</sup>, 振动加速度从 0.8 g 降至 0.3 g, 降幅 62%, EMC 测试, 电源波动 9~15 V 正常工作, 辐射抗扰 10 V/m 通过 IEC61000-4-3 三级, ESD  $\pm 6$  kV/ $\pm 8$  kV 通过四级, EFT  $\pm 4$  kV/ $\pm 2$  kV 通过四级[15]。环境测试, -10°C ~+60°C 运行 72 小时精度漂移  $< 5\%$ , 振动 1 g/2 小时功能正常, 240 小时连续运行无故障, FPGA 温度 78°C, 定位精度波动  $\pm 0.5 \mu$ m。

### 4.3. 优化效果对比与分析

与传统 ARM 单核方案对比测试，性能提升量化如表 1。

**Table 1.** Performance comparison between optimized scheme and traditional scheme

**表 1.** 优化方案与传统方案性能对比

| 性能指标                     | 传统方案 | 优化方案  | 提升幅度    |

|--------------------------|------|-------|---------|

| 插补周期(μs)                 | 1000 | 50    | -95%    |

| 电流环周期(μs)                | 100  | 10    | -90%    |

| 六轴联动精度(μm)               | ±8   | ±2    | +75%    |

| 通信抖动(μs)                 | 218  | 0.085 | -99.96% |

| 指令响应(ms)                 | 2.5  | 0.05  | -98%    |

| 整机功耗(W)                  | 26   | 18.5  | -29%    |

| PCB 面积(cm <sup>2</sup> ) | 180  | 117   | -35%    |

| MTBF(小时)                 | 3500 | 8200  | +134%   |

优化方案在所有关键指标均显著提升。插补周期缩短 20 倍源于 FPGA 硬件加速，电流环周期缩短 10 倍改善动态性能，联动精度提升 75% 达高端水平。通信抖动降低 99.96% 体现硬件协议栈优势，功耗降低 29% 得益于高效电源管理，PCB 面积减小 35% 源于 SoC 高集成度，MTBF 提升 134% 归功于可靠性设计。

成本效益分析如表 2。

**Table 2.** Cost-benefit analysis of optimization scheme

**表 2.** 优化方案成本效益分析

| 成本项目    | 传统方案(元) | 优化方案(元) | 变化          |

|---------|---------|---------|-------------|

| 主控芯片    | 360     | 480     | +120        |

| 其他器件    | 685     | 575     | -110        |

| PCB 制造  | 450     | 320     | -130        |

| 装配测试    | 200     | 150     | -50         |

| BOM 总成本 | 1695    | 1525    | -170 (-10%) |

虽然 Zynq SoC 单价较高，但通过减少外围器件，简化 PCB，降低装配成本，BOM 总成本下降 10% [16]。性能提升数倍且可靠性提高使维护成本大幅降低，生命周期总成本优势明显，对标国际产品，优化方案插补周期 50 μs，定位精度 ±2 μm，通信抖动 < 100 ns，功耗 18.5 W 等指标达到国际中高端水平，部分指标超越进口产品。

### 4.4. 关键硬件优化实现详述

#### 4.4.1. 50 μs 插补周期的 FPGA 流水线实现

为实现 50 μs 的超高速插补周期，设计了五级流水线结构，(1) 指令解码级，将 G 代码解析为插补参数，延迟 150 ns，(2) 参数预处理级，完成坐标变换与速度规划，延迟 8 μs，(3) 插补计算级，采用 Bresenham 算法的并行改进版本，6 个轴的脉冲计算同时进行，单周期延迟 200 ns，(4) S 曲线加减速级，采用 7 段式加加速度控制，查找表深度 512，延迟 1.2 μs，(5) 脉冲输出级，通过双端口 RAM 缓冲 128 个脉冲点，保证输出连续性。

流水线时序设计中，各级之间通过 FIFO 解耦，深度分别设为 16/32/64/32，在 125 MHz 主时钟下，理论吞吐率可达 8 ns/点。实际测试中，连续直线插补的周期抖动标准差为 3.2 ns，圆弧插补为 8.5 ns，样条曲线为 15.7 ns，均满足 < 50 ns 的设计要求。FPGA 资源占用方面，该模块消耗 28% 的逻辑单元(23.8 K/85 K)，45% 的 DSP Slice (99/220)，18% 的 BRAM (36/140)，为其他功能模块预留了充足空间。

#### 4.4.2. 关键器件选型论证

关键器件选型经过多方案对比论证，具体如表 3 所示。

**Table 3.** Comparison of key device selection

**表 3. 关键器件选型对比**

| 器件类型    | 备选方案 A                                | 备选方案 B                             | 最终选择及理由                                                                                        |

|---------|---------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------|

| SoC     | Intel Cyclone V SoC<br>(A9 双核 + FPGA) | Xilinx Zynq-7020<br>(A9 双核 + FPGA) | 选择 Zynq-7020：AXI4 总线带宽 1200 MB/s 优于 Cyclone V 的 800 MB/s；工具链成熟度高；功耗 18.5 W 低于 Cyclone V 的 23 W |

| Buck 芯片 | LT3845 (单路 15A)                       | TPS53355 (双路 30A)                  | 选择 TPS53355：双路并联提供 30A 满足 FPGA 峰值需求；瞬态响应 8 μs 优于 LT3845 的 15 μs；集成度高减少外围器件                     |

| 光耦      | TLP281 (80 ns 延迟)                     | 6N137 (50 ns 延迟)                   | 选择 6N137：延迟低 37.5%，共模瞬态抗扰 15 kV/μs 优于 TLP281 的 10 kV/μs，满足工业 4 kV ESD 要求                       |

#### 4.4.3. 关键性能测试方法

(1) 插补周期测试，使用 Tektronix MDO4104 示波器(带宽 1 GHz，采样率 5 GSa/s)监测 FPGA 引脚 PL\_CLK\_OUT，该引脚在每个插补周期开始时产生 200 ns 正脉冲。连续采集 10,000 个周期，计算标准差与最大偏差。测试平台为六轴龙门式平台，工作台尺寸 600 mm × 400 mm × 200 mm，丝杠导程 10 mm，细分数 10,000。

(2) 轨迹精度测试，采用 Renishaw XL-80 激光干涉仪(分辨率 1 nm，测量范围 80 m)进行 21 点双向定位精度测试，符合 ISO 230-2:2014 标准。圆弧插补精度使用 API XD Laser (角度测量精度±0.5")的圆度测试功能，在 XY 平面绘制直径 100 mm 的圆，测量 360 个点的径向误差。

(3) 功耗测试，使用 Keysight N6705B 直流电源分析仪(电流测量精度 0.025% + 500 μA)分别监测各路电源的实时功耗，测试工况包括空闲，轻载(单轴 500 mm/min)，重载(六轴联动 2000 mm/min)三种状态，每种状态持续 10 分钟后记录平均功耗。

### 5. 结语

该研究采用 ARM + FPGA 异构架构，分级电源拓扑，差分隔离接口，信号完整性优化等技术，系统性解决了多轴运动控制器实时性不足，功耗偏高和电路复杂的技术难题。硬件加速使插补周期从 1 ms 缩短至 50 μs，提升 20 倍，电流环周期从 100 μs 缩短至 10 μs，提升 10 倍。动态电压调节使整机功耗从 26 W 降至 18.5 W，降低 29%，EMC 优化使 MTBF 从 3500 小时提升至 8200 小时，提升 134%。六轴联动精度达±2 μm，PCB 面积减小 35%，主要性能达到国际中高端水平。未来研究将聚焦国产芯片替代，智能算法融合，TSN 时间敏感网络应用三个方向，为高精度数控装备国产化提供核心技术支撑。

### 参考文献

- [1] 张一东, 徐一栋, 陈海卫. 基于 PCIe 总线的机器人多轴控制器的研究[J]. 机床与液压, 2024, 52(21): 35-42.

-

- [2] 关建文, 陈占军, 王连明, 等. 基于 SOC 的步进电机多轴运动控制器的设计[J]. 现代电子技术, 2022, 45(7): 163-167.

- [3] 郭风祥, 徐国伟, 宋庆增, 等. 基于 Zynq 的多轴控制系统[J]. 国外电子测量技术, 2021, 40(11): 130-134.

- [4] 姚必根. 自动化弯管机多轴运动控制系统设计研究[J]. 装备制造技术, 2024(3): 168-171.

- [5] 王俊杰, 陈国兴, 步石, 等. 多轴精密运动台前馈控制器参数整定方法[J]. 电子工业专用设备, 2023, 52(6): 67-73.

- [6] Zhou, R., Wang, Z., Lu, J., Zhu, Y. and Hu, C. (2025) Ultraprecision Multi-Axis CARIC Control Strategy with Application to a Nano-Accuracy Air-Bearing Motion Stage. *ISA Transactions*, **158**, 572-585.

<https://doi.org/10.1016/j.isatra.2025.01.020>

- [7] Zhang, J., Xia, M., Li, H., Li, S. and Shi, J. (2024) The Design and Real-Time Optimization of an Ethercat Master for Multi-Axis Motion Control. *Electronics*, **13**, Article 3101. <https://doi.org/10.3390/electronics13153101>

- [8] Gutierrez, H. and Li, D. (2024) Nonlinear Passive Observer for Motion Estimation in Multi-Axis Precision Motion Control. *Machines*, **12**, Article 376. <https://doi.org/10.3390/machines12060376>

- [9] Jiang, J., Li, B., Dong, Q., Zhang, H., Ye, P. and Jiang, S. (2023) Contour Error Dynamic Analysis and Predictive Control for Multi-Axis Motion System. *The International Journal of Advanced Manufacturing Technology*, **126**, 5501-5514.

<https://doi.org/10.1007/s00170-023-11415-z>

- [10] Hao, R. (2022) Application of S7-300 PLC and Single Axis Motion Controller in Manipulator Control System. *Journal of Physics: Conference Series*, **2200**, Article ID: 012006. <https://doi.org/10.1088/1742-6596/2200/1/012006>

- [11] Liu, T., Mao, H., Lei, D., Li, B. and Fu, D. (2021) A Study on Intelligent GIS Installation System Based on Six-DOF Parallel Multi-Axis Motion Control. *Journal of Physics: Conference Series*, **2074**, Article ID: 012066.

<https://doi.org/10.1088/1742-6596/2074/1/012066>

- [12] Wang, S., Chen, Y. and Zhang, G. (2021) Adaptive Fuzzy PID Cross Coupled Control for Multi-Axis Motion System Based on Sliding Mode Disturbance Observation. *Science Progress*, **104**.

<https://doi.org/10.1177/00368504211011847>

- [13] Zhu, J., Zhou, Q., Wu, L., Xu, J. and Wang, X. (2021) Topology Reconstruction Based Fault Identification for Uncertain Multi-Agent Systems with Application to Multi-Axis Motion Control System. *Applied Mathematics and Computation*, **399**, Article ID: 126000. <https://doi.org/10.1016/j.amc.2021.126000>

- [14] Al-Rawashdeh, Y.M., Al-Tamimi, M., Heertjes, M. and Janaideh, M.A. (2021) Micro-Positioning End-Stage for Precise Multi-Axis Motion Control in Optical Lithography Machines: Preliminary Results. 2021 American Control Conference (ACC), New Orleans, 25-28 May 2021, 40-47. <https://doi.org/10.23919/acc50511.2021.9483343>

- [15] Sousy, E.M.F.F. (2021) Robust Hybrid Control Using Recurrent Wavelet- Neural-Network Sliding-Mode Controller for Two-Axis Motion Control System. *International Journal of Neural Networks and Advanced Applications*, 849-859.

- [16] Yao, S.H., Gao, G.Q. and Gao, Z.Q. (2020) On Multi-Axis Motion Synchronization: The Cascade Control Structure and Integrated SMC-ADRC Design. *ISA Transactions*, **109**, 259-268.