# 基于时钟树机制的高相位分辨率矢量 信号源研究

邱 亮1,2\*, 宋昊东1,2, 潘朝松1,2, 廉 哲1,2, 朱亦鸣1,2

1上海理工大学光电信息与计算机工程学院,上海

收稿日期: 2025年7月7日; 录用日期: 2025年8月19日; 发布日期: 2025年8月28日

# 摘要

在高速矢量信号源系统架构中,并行交织输出的数模转换器(Digital-to-Analog Converter, DAC)结构虽被广泛应用于缓解采样速率与采样精度之间的固有矛盾,但系统极易受各通道采样时钟抖动的影响。本文分析了采样时钟抖动与采样有效位数之间的关系,设计了一种基于时钟树机制的并联DAC交织输出结构的高相位分辨率矢量信号源系统。实验验证结果表明,在相同的测试条件下,相较于传统单块DAC矢量信号源系统,所提系统的输出速率提升了4倍,信噪比实现了约4.5 dB的提高。

## 关键词

高相位分辨率,数模转换,并行交织输出,信噪比

# Research on High Phase Resolution Vector Signal Source Based on Clock Tree Mechanism

Liang Qiu<sup>1,2\*</sup>, Haodong Song<sup>1,2</sup>, Chaosong Pan<sup>1,2</sup>, Zhe Lian<sup>1,2</sup>, Yiming Zhu<sup>1,2</sup>

<sup>1</sup>School of Optical-Electrical and Computer Engineering, University of Shanghai for Science and Technology, Shanghai

<sup>2</sup>Semight Instruments Co., Ltd., Suzhou Jiangsu

Received: Jul. 7<sup>th</sup>, 2025; accepted: Aug. 19<sup>th</sup>, 2025; published: Aug. 28<sup>th</sup>, 2025

#### **Abstract**

In the architecture of high-speed vector signal generator systems, the parallel interleaved Digital\*通讯作者。

文章引用: 邱亮, 宋昊东, 潘朝松, 廉哲, 朱亦鸣. 基于时钟树机制的高相位分辨率矢量信号源研究[J]. 软件工程与应用, 2025, 14(4): 938-947. DOI: 10.12677/sea.2025.144083

<sup>2</sup>苏州联讯仪器股份有限公司, 江苏 苏州

to-Analog Converter (DAC) structure is widely employed to mitigate the inherent trade-off between sampling rate and sampling precision. However, such systems are highly susceptible to the impact of sampling clock jitter across multiple channels. This paper analyzes the relationship between sampling clock jitter and the Effective Number of Bits (ENOB). A high-phase-resolution vector signal generator system based on a clock tree-mechanized parallel DAC interleaved output structure is proposed. Experimental validation results demonstrate that, under identical test conditions, the proposed system achieves a fourfold increase in output rate and an approximately 4.5 dB improvement in Signal-to-Noise Ratio (SNR) compared to the traditional single-DAC vector signal generator system.

## **Keywords**

High-Phase-Resolution, Digital-to-Analog Conversion, Parallel Interleaved Output, Signal-to-Noise Ratio

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

http://creativecommons.org/licenses/by/4.0/

Open Access

# 1. 引言

矢量信号源系统是一种基于精密相位控制与直接数字合成技术(DDS)的先进信号生成设备,它依托高精度数模转换(DAC)技术,实现了对信号相位、幅度及频率的精细调控与输出。DAC可用于将数字信号转换成模拟信号。其接口作为独立的数模转换芯片用于信号处理,可用于 DDS 中将数字转换成模拟信号输出。由奈奎斯特采样定理可知,采样频率必须大于信号中最高频率的两倍,才能够不失真的还原信号,该定理同样适用于 DAC 中,DAC 的输出速率必须大于其输出信号的两倍,输出的模拟信号才不至于过度失真。这就对 DAC 的各项性能指标,如采样率、分辨率、信噪比、抗于扰能力等有更高的要求[1][2]。

针对提高系统的采样率与分辨率,庄怡提出了一种混合交替采样(QIADC)系统分析及分辨率优化方法[3],该方法的有效位数约提升了1 bit,混合交替采样系统的有效位数提升了约 0.6 bit。雷雯提出了一种基于四路 ADC 芯片交替采样的宽带信号采集系统设计[4],在 440 MHz 到 6140 MHz 频率范围内,该系统的有效位大于 7.2 bit,无杂散动态范围大于 51 dB。

本文设计了一种基于时钟树机制、并行 DAC 交织输出结构的高相位分辨率矢量信号源系统。利用时钟树结构生成多路协调 DAC 交织输出的时钟信号实现了一个高性能交织 DAC 系统的设计,时钟树结构包含抖动衰减功能、内部压控振荡源和多个同步管理功能,可以对多路 DAC 的采样时钟分别进行稳频和严格锁相,减小采样时钟抖动引起的转换误差及畸变,最大限度保留原单片 DAC 的高精度指标[5]。从而解决了传统数字系统以牺牲输出精度换取输出速率的弊端,实现了相对单片 DAC 矢量信号源系统最高输出速率 500 MHz 的提升以及约 4.5 dB 信噪比的提高。

## 2. 时钟抖动分析

#### 2.1. DAC 输出率分辨率关系

数模转换系统中,采样率与分辨率存在固有矛盾。受奈奎斯特采样定理约束,分辨率的提升需延长转换时间,而采样率提高则要求缩短单次转换周期,这导致单片 DAC 架构难以同时满足高精度与高速度需求。为突破这一瓶颈,现行主流方案是并行多片低速高分辨的 DAC 芯片做模拟信号输出[6]。该架构

下,各通道同步采样同一输入信号,通过采样率叠加,一方面实现采样率的提高,另一方面也可以保持单块 DAC 芯片的分辨率性能。但在实际应用中,每个采集通道的增益性能与偏置电压会因工艺的问题产生误差,且提供的时钟信号本身也存在一定的抖动,导致各通道时钟延迟发生偏斜[7]。时基失配主要由时钟分布网络延迟差异引起,时基失配因具有随机性特征,成为制约系统性能的关键因素。时钟抖动产生的采样时间不确定性,会直接导致信号重构失真,尤其在高频段表现更为显著[8]。因此,抑制时钟抖动成为提升并行采样系统性能的核心技术路径。

## 2.2. 时钟抖动对输出信号的影响

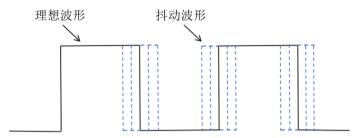

时钟信号的品质通常由时钟抖动与相位噪声表征,两者分别对应着时域和频域[9]。如图 1 所示,图中实线表示理想时钟波形,其边沿是等间隔的。虚线表示理想时钟波形存在跳变,这种抖动的不确定性是引起时钟抖动的主要原因。

Figure 1. Schematic diagram of aperture jitter 图 1. 孔径抖动示意图

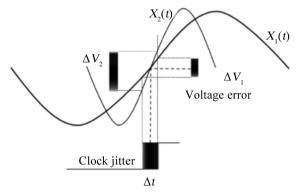

在实际应用中时钟抖动是极其微小的,如图 2 所示,对于不同频率、相同信号强度的模拟信号  $X_1$  (t) 和  $X_2$  (t),对于同一个时钟抖动 $\Delta$ t 来说,误差 $\Delta$ V<sub>2</sub> 明显大于 $\Delta$ V<sub>1</sub>。即输出频率越高,时钟抖动导致的 DAC 输出误差也将越大。

Figure 2. Amplitude quantization deviation caused by output clock jitter 图 2. 输出时钟抖动导致幅度量化偏差图

下面分析有效位数的影响因素,首先信噪比[10]公式为

$$SNR = 20\log\frac{1}{2\pi f_{\text{condex}}t_{\text{interes}}}\tag{1}$$

其中 $f_{analog}$ 是输入信号的频率, $t_{jitter}$ 时时钟的抖动有效值。

由公式(1)得, $f_{analog}$ 和  $t_{iitter}$ 直接影响系统的信噪比。理想 DAC 的信噪比与 DAC 的位数关系用分贝可

表示为:

$$SNR = 6.02N + 1.76 \tag{2}$$

信噪失真比为:

$$SINAD = \frac{P_{signal}}{P_{noise} + P_{distartion}} \tag{3}$$

其中  $P_{signal}$ 、 $P_{noise}$ 、 $P_{distortion}$  分别为信号功率,噪声功率和谐波失真功率。DAC 的有效位数为:

$$ENOB = \frac{\left(SINAD - 1.76\right)}{6.02} \tag{4}$$

若不考虑谐波失真, SINAD 的理论值可近似等于信噪比,则有效位数与信噪比的关系为:

$$ENOB \approx \frac{\left(SNR - 1.76\right)}{6.02} \tag{5}$$

将式(1)带入式(5),可得到有效位数与时钟抖动的关系:

$$ENOB \approx \frac{20\log\frac{1}{2\pi f_{ana\log t_{jitter}}} - 1.76}{6.02}$$

(6)

由式(6)可知, 当时钟抖动越大时, 有效位数越低。

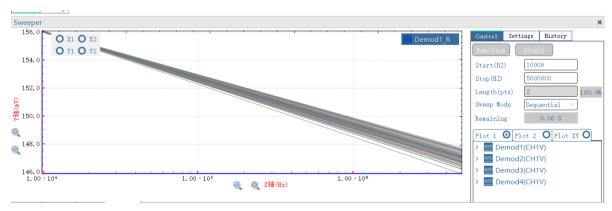

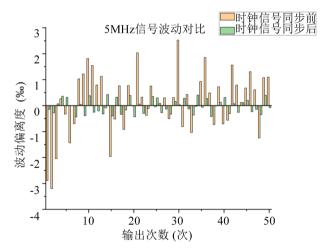

传统矢量信号源系统的 DAC 工作时钟是由 CPU 内部晶振时钟通过 PLL 分频得到,分频出来的时钟信号本身会存在一定的抖动,当 DAC 输出时,每个 DAC 的输出时钟信号无法精确同步,将会导致输出信号出现相位误差。这种相位误差将导致输出结果上下浮动,同时随着 DDS 输出信号频率的升高,信号的周期变短,相同时间内信号波形经历的相位变化增加。此时若输出时钟与 DDS 参考时钟的相位差保持不变,那么相位偏移就会随着频率的升高而变大。如图 3 所示,矢量信号源系统输出一个 430 mV 正弦波信号,并将输出频率在 10 kHz 与 5 MHz 之间来回切换。可看出 100 次输出中,5 MHz 下最大波动为 1.8 mV。该误差的波动范围对于一个稳定的矢量信号源系统是不允许的。

Figure 3. Schematic diagram of output fluctuations under unsynchronized output clock 图 3. 未同步输出时钟下的输出波动示意图

# 3. 并行 DAC 交替采样设计

## 3.1. 并行 DAC 输出设计

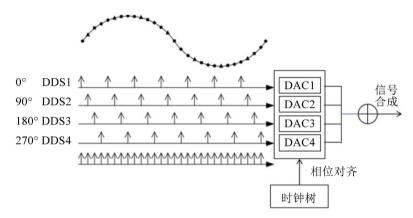

本文通过采用并行四块 AD9117 芯片交替输出,实现对输出速率的提升。AD9117 是 Analog Devices

Inc (ADI)推出的一款高性能 DAC 芯片。其分辨率为 14 bit,采样速率 125 MSPS。如图 4 所示,通过使用 4 个 DDS 直接数字合成器,以延迟相位的方式从波形存储器中读取数据并输出到四个同步时钟的 DAC 中。4 个 DDS 分别以一个固定的相位差同时从波形存储器中读取数据,每个 DDS 的时钟频率保持一致,相位依次相差 90 度,即读取的各数据在相位上是交错排列的,然后将各自读取的数据传输到对应的 4 块 DAC 芯片上,最终 DAC 芯片将同一时刻采集到的数据通过加法器进行相应的交替式整合输出,同时采用了时钟树结构生成多路时钟信号为 DAC 提供输出时钟。采用这样的方法,可以将整个系统的输出速率提高为单片 DAC 输出速率的四倍,并保留着原单片 DAC 的高输出精度[11],理论上解决了高采样率和高分辨率的矛盾。

Figure 4. Schematic diagram of alternate output in parallel DACs 图 4. 并行 DAC 交替输出示意图

#### 3.2. 时钟树设计

在并行 DAC 交织输出架构中,设计多通道低抖动采样时钟系统对于保障系统性能至关重要。在常规实现方案里,协调多路 DAC 协同工作的时钟信号通常借助时钟分配芯片来生成。从硬件实现角度来看,该方式具有相对简便的优势。然而,在实际电路板设计阶段,PCB 的布线布局以及电子元器件自身存在的制造误差等因素,均会致使输出的时钟信号不可避免地产生一定程度的抖动,进而显著增加了时钟信号的不确定性。此外,这些电子元器件极易受到外界环境因素的干扰,例如电源电压的波动、工作温度的变化,以及特定器件在制造工艺过程中存在的工艺偏差等,这些因素同样会进一步加剧时钟信号的不确定性,最终将导致 DAC 的时序出现偏差。对于对时钟信号精度要求极为严苛的并行 DAC 结构而言,这种时序偏差是难以容忍的,会严重影响整个系统的性能与稳定性[12] [13]。

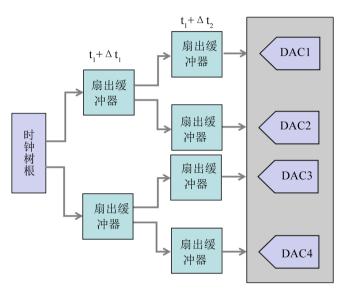

针对多通道并行 DAC 系统对低抖动、高精度时钟信号的需求,本文设计了一种基于时钟树结构的时钟信号生成方案。该时钟树拓扑结构如图 5 所示,其核心架构由时钟树树根与多级缓冲器级联构成,展现出高度的灵活性与可扩展性,能够依据实际应用场景的需求,灵活配置时钟信号输出通道的数量。在时钟树结构中,各级引入了确定性时间误差(如图中  $t_1$ 、 $t_2$  所示)与不确定性时间误差( $\Delta t_1$ ,  $\Delta t_2$ )。其中,确定性时间误差源于时钟树各组件固有的时序特性,可通过后期数据处理算法进行精确校正;而不确定性时间误差则由 PCB 布线寄生参数、元器件性能波动以及环境干扰等多种因素共同作用产生,在传统基于时钟分配芯片的方案中,此类不确定性误差难以得到有效抑制。

对此本文选用 ADI 公司的高性能双环路整数 N 分频抖动衰减器 HMC7044 作为时钟树的树根节点。该芯片支持通过上位机软件发送串行外设接口(SPI)命令或同步请求脉冲(SYNC)信号,实现对输出时钟信号相位的精确对齐。在此过程中,芯片内置的通用参考信号定时器将同步复位,进而确保所有时钟输出

分频器实现高精度同步。此外,HMC7044 还支持通过上位机软件设置生成特定数量的输出脉冲,作为系统内部的参考信号脉冲,为多通道时钟信号的同步提供了可靠的基准。本文方案能够有效补偿各级输出之间的偏斜误差,以及因后期制板过程中各输出端线路长度不一致所导致的误差。所提出的时钟树结构显著降低了时钟信号的不确定性误差,为并行 DAC 系统提供了高精度、低抖动的时钟信号保障[14]。

Figure 5. Clock tree topology diagram 图 5. 时钟树拓扑图

# 4. 实验结果

## 4.1. 时钟树结构仿真及实验测试

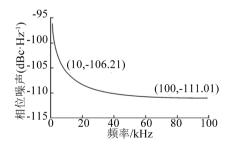

利用 EDA 软件 ADIsimCLK 对 HMC7044 进行仿真,具体参数设置如下:输出信号为 128.88 MHz, 32 倍时钟分频,单通道输出的时钟信号频率为 100 MHz。仿真结果如图 6 所示,在并行 DAC 输出结构的应用场景下,时钟信号在 10 kHz~20 MHz 频带范围内的抖动情况对系统性能具有关键影响。基于此,本研究选取 10 kHz 和 100 kHz 这两个具有代表性的频率点,对仿真结果中的相位噪声进行计算,分别为 -106.21 dBc/Hz 和-111.01 dBc/Hz。

Figure 6. Simulation results of phase noise for a 100 MHz signal 图 6. 100 MHz 信号相位噪声仿真结果

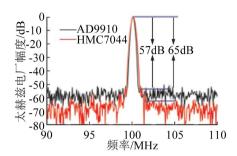

同时采用频谱分析仪对输出的单通道 100 MHz 时钟信号进行了相位噪声测试,结果如图 7 所示。可知在 10 kHz 和 100 kHz 处的相位噪声分别为-97 dBc/Hz 和-107 dBc/Hz。由于实际设计中 PCB 板的布线、焊接及测量误差等因素的影响,HMC7044 相位噪声的实际测试数据比图 6 的仿真结果稍差一点,但

基本符合预期结果。

接着进一步将其与采用锁相环时钟芯片 AD9910 的方案进行了对比测试。对比结果如图 7 所示。相较 AD9910 的时钟信号生成方案,本文所提出的时钟树结构展现出更低的相位噪声和更小的时钟抖动。这一优势表明,将该时钟树结构应用于并行 DAC 交织输出结构中,能够显著提升高相位分辨率矢量信号源系统的有效位数和分辨率,为高性能信号处理系统的设计提供了有力的技术支持。

Figure 7. Phase noise 图 7. 相位噪声

# 4.2. 输出偏离度测试

DDS 输出峰峰值为 1000 mV 的正弦波信号,在 100 kHz 与 5 MHz 之间来回切换输出,输出的波动结果对比如图 8 所示。图 8 所示为同步时钟信号前后 DDS 输出信号切换回 5 MHz 采集 100 次的输出偏离度对比结果。测试表明,输出信号的频率越高,对应同步时钟信号后的效果也越好。在输出信号频率 5 MHz 的情况下,波动离散度由 5.7‰提升到了 0.08‰。

**Figure 8.** Comparison of 5 MHz output deviation before and after clock signal synchronization 图 8. 时钟信号同步前后 5 MHz 输出偏离度对比

## 4.3. 输出信噪比与分辨率对比测试

时钟树同步 DAC 输出时钟后,对单个 DAC 和并行 DAC 输出进行信噪比和有效分辨率进行对比,图 9 所示为通过 DDS 输出不同频率的波形,在 ila 中抓取的原始数据结果。

AD9117 的采样率为 125 M,将四块 AD9117 行交替输出,采样率可达 500 M。将单片 DAC 系统的采样率设置为 125 M,并行 DAC 系统的采样率设置为 500 M,分别输出 60 M,20 M,2 M 正弦波信号,

在 Vivado 中通过 ila 在线逻辑分析仪对 DAC 输出信号进行抓取,得到结果如图 9(a)~(f)。其中如图 9(a) 和图 9(b)所示,输出频率为 60 MHz 时,并行 DAC 的抓取波形有一定的失真,单块 DAC 的抓取波形失真非常严重,已经达到奈奎斯特定理的极限范围;图 9(c)和图 9(d)所示,输出频率为 20 MHz 时,并行 DAC 的抓取波形较为平滑,单块 DAC 的抓取波形仍存在较为明显的失真;图 9(e)和图 9(f)所示,输出频率为 2MHz 时,并行 DAC 与单块 DAC 的抓取波形都较为平滑。

**Figure 9.** Schematic diagram of output sine waves at 60 M, 20 M, and 2 MHz captured by an ILA (Integrated Logic Analyzer) for parallel DACs and a single DAC

图 9. ILA 在线逻辑分析仪抓取并行 DAC 与单块 DAC 输出 60 M, 20 M, 2 MHz 正弦波示意图

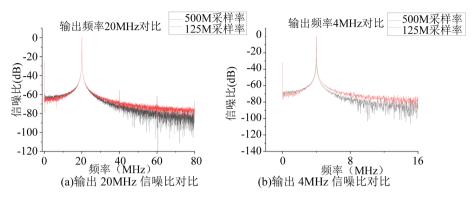

然后将 DAC 交替输出与单个 DAC 输出的原始数据导出作 FFT 频谱分析,具体结果如图 10(a)和图 10(b)所示。可知并行 DAC 输出信号的信噪比整体上要比单片 DAC 输出的信噪比高 4~5 dB。

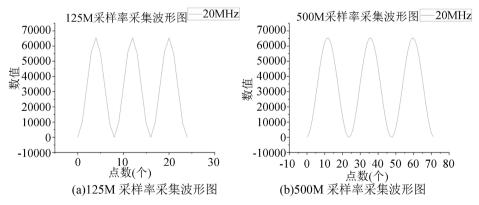

将单块 AD9117 输出的数据导出,在 Origin 中对输出数据做 FFT 频谱分析,通过 FFT 数据可计算出对应频率下的信噪比和有效位数,具体结果如表 1 所示。同时将输出信号 20 MHz 时的原始数据放入 Origin 中作出对应模拟波形,结果如图 11(a)所示。图 11(a)中可看到三个周期的正弦波信号,采样点数为 6.25 个,此时系统整体采样率为 125 MSPS,信噪比为 67.5672 dB,有效位数 ENOB 为 10.9314 bit。

将并行 AD9117 输出的数据导出,在 Origin 中对输出数据做 FFT 频谱分析,通过 FFT 数据可计算出对应频率下的信噪比和有效位数,具体结果如表 2 所示。同时将输出信号 20 MHz 时的原始数据放入 Origin 中作出对应模拟波形,结果如图 11(b)所示。图 11(b)中可看到三个周期的正弦波信号,采样点数为

25 个,与单块 DAC 输出相比,输出率提高了 4 倍,此时系统整体采样率为 500 MSPS,信噪比为 71.8487 dB,有效位数 ENOB 为 11.6426 bit。

**Figure 10.** Comparison of Signal-to-Noise Ratio (SNR) between alternate output of DACs and output of a single DAC at 20 MHz and 4 MHz

图 10. DAC 交替输出与单个 DAC 输出 20 MHz 和 4 MHz 下信噪比对比

Table 1. Sampling performance indicators of a single DAC 表 1. 单个 DAC 采样性能指标

| 频率         | 800 kHz | 2 MHz   | 4 MHz   | 8 MHz   | 20 MHz  |

|------------|---------|---------|---------|---------|---------|

| 周期点数       | 156.25  | 62.5    | 31.25   | 15.625  | 6.25    |

| 采样率(MSPS)  | 125     | 125     | 125     | 125     | 125     |

| SNR (dB)   | 67.6428 | 67.3586 | 67.5238 | 68.1083 | 67.5672 |

| ENOB (bit) | 10.9439 | 10.8967 | 10.9242 | 11.0213 | 10.9314 |

Table 2. Alternate sampling performance indicators of parallel DACs 表 2. 并行 DAC 交替采样性能指标

| 频率        | 800 kHz | 2 MHz   | 4 MHz   | 8 MHz   | 20 MHz  |

|-----------|---------|---------|---------|---------|---------|

| 周期点数      | 625     | 250     | 125     | 62.5    | 25      |

| 采样率(MSPS) | 500     | 500     | 500     | 500     | 500     |

| SNR(dB)   | 71.7592 | 71.5675 | 71.2425 | 71.9592 | 71.8487 |

| ENOB(bit) | 11.6277 | 11.5959 | 11.5419 | 11.6609 | 11.6426 |

Figure 11. Waveform diagrams collected at 125 M and 500 M sampling rates 图 11. 125 M 采样与 500 M 采样率采集波形图

由上述实验可以得出,并行 DAC 交织输出系统能够实现在提高输出采集速率的同时,对原单片 DAC 的精确度也有一定的提升。

## 5. 结论

本文分析了输出时钟的相位噪声对并行 DAC 交织输出结构有效位数的影响。提出了基于时钟树结构生成分布输出时钟的方法,相比于利用锁相环时钟芯片产生信号的方案,时钟树结构具有更小的时钟抖动,保证了在极大提高输出速度的前提下,最大限度的保证了高分辨率,改进了传统高速矢量信号源系统以牺牲输出精度换取输出速率的弊端。结果表明,基于时钟树机制、并联 DAC 交织输出结构的高相位分辨率矢量信号源系统,有效解决了数模转换机制中分辨率与采样率不能同时兼顾的矛盾,实现了最高采样率 500 MHz、信噪比约 4.5 dB 的提高。这对于设计更高速的高相位分辨率矢量信号源具有非常重要的工程意义。

# 基金项目

本文的研究已受到国家重点研发计划"基础科研条件与重大科学仪器设备研发专项"——半导体器件动态伏安特性参数综合测试仪(项目编号 2023YFF0717900)的资助。

# 参考文献

- [1] Mitola, J. (1995) The Software Radio Architecture. *IEEE Communications Magazine*, **33**, 26-38. https://doi.org/10.1109/35.393001

- [2] Kurosawa, N., Kobayashi, H., Maruyama, K., Sugawara, H. and Kobayashi, K. (2001) Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems. *IEEE Transactions on Circuits and Systems I: Fundamental The*ory and Applications, 48, 261-271. <a href="https://doi.org/10.1109/81.915383">https://doi.org/10.1109/81.915383</a>

- [3] 庄怡. 混合交替采样系统分析及分辨率优化方法实现[D]: [硕士学位论文]. 成都: 电子科技大学, 2021.

- [4] 雷雯, 栗敬雨. 基于四路 ADC 芯片交替采样的宽带信号采集系统设计[J]. 电子科技, 2021, 34(9): 30-35.

- [5] Huang, S. and Levy, B.C. (2007) Blind Calibration of Timing Offsets for Four-Channel Time-Interleaved ADCs. *IEEE Transactions on Circuits and Systems I: Regular Papers*, **54**, 863-876. <a href="https://doi.org/10.1109/tcsi.2006.888770">https://doi.org/10.1109/tcsi.2006.888770</a>

- [6] Kurosawa, N., Kobayashi, H., Maruyama, K., Sugawara, H. and Kobayashi, K. (2001) Explicit Analysis of Channel Mismatch Effects in Time-Interleaved ADC Systems. *IEEE Transactions on Circuits and Systems I: Fundamental The*ory and Applications, 48, 261-271. https://doi.org/10.1109/81.915383

- [7] Nassiri, M.I. and Rezvanyvardom, M. (2018) A New Adaptive Blind Background Calibration of Gain and Timing Mismatch for a Two-Channel Time-Interleaved ADC. *Microelectronics Journal*, 77, 26-33. https://doi.org/10.1016/j.mejo.2018.05.008

- [8] Zhao, L., Jiang, Z., Dong, R., Cao, Z., Gao, X., Cheng, B., et al. (2018) An 8-Gs/s 12-Bit TIADC System with Real-Time Broadband Mismatch Error Correction. IEEE Transactions on Nuclear Science, 65, 2892-2900. https://doi.org/10.1109/tns.2018.2878875

- [9] Immink, K.A.S. and Weber, J.H. (2014) Minimum Pearson Distance Detection for Multilevel Channels with Gain And/or Offset Mismatch. *IEEE Transactions on Information Theory*, 60, 5966-5974. <a href="https://doi.org/10.1109/tit.2014.2342744">https://doi.org/10.1109/tit.2014.2342744</a>

- [10] Brannon, B. (2004) Understand the Effects of Clock Jitter and Phase Noise on Sampled Systems. EDN-Boston then Denver then Highlands Ranch Co., 49, 87-96.

- [11] Kong, D. and Galton, I. (2018) Adaptive Cancellation of Static and Dynamic Mismatch Error in Continuous-Time Dacs. *IEEE Transactions on Circuits and Systems I: Regular Papers*, **65**, 421-433. <a href="https://doi.org/10.1109/tcsi.2017.2737986">https://doi.org/10.1109/tcsi.2017.2737986</a>

- [12] Elbornsson, J., Gustafsson, F. and Eklund, J.-E. (2005) Blind Equalization of Time Errors in a Time-Interleaved ADC System. *IEEE Transactions on Signal Processing*, **53**, 1413-1424. <a href="https://doi.org/10.1109/tsp.2005.843706">https://doi.org/10.1109/tsp.2005.843706</a>

- [13] 朱志东、邹月娴、陶阁. 一种宽带高性能 TIADC 时钟发生器门[J]. 数据采集与处理、2009、14(S1): 177-181.

- [14] Fakhfakh, A., Milet-Lewis, N., Deval, Y. and Levi, H. (2001) Study and Behavioural Simulation of Phase Noise and Jitter in Oscillators. ISCAS 2001. The 2001 IEEE International Symposium on Circuits and Systems, Sydney, 6-9 May 2001, 323-326. https://doi.org/10.1109/iscas.2001.922050