# 基于数智化的FPGA检测技术研究

易 忠,李星毅,朱 洪,宋建磊

贵州航天计量测试技术研究所,贵州 贵阳

收稿日期: 2025年9月15日; 录用日期: 2025年10月13日; 发布日期: 2025年10月23日

#### 摘要

传统元器件检测方法依赖人工目检和单点功能测试,存在误差率大、覆盖率不足、效率低下等局限性,尤其在高密度FPGA、SOC芯片中,测试周期和成本已成为制约装备交付的关键瓶颈。在此技术困境下,数智化技术凭借数据驱动决策、智能协同处理的核心优势,正逐步重塑元器件检测领域的技术范式,推动该领域从传统人工主导模式向智能化、数字化方向加速转型,当前已进入技术迭代的关键窗口期。本文系统探讨了元器件检测技术面临的挑战与创新路径,结合机器学习、边缘计算等前沿检测技术,重点研究了FPGA测试的智能化解决方案。同时,基于元器件检测技术的发展,对当前FPGA测试流程做了优化,旨在外观检测、配置程序、测试向量方面进行速度和精度方面的提升。

#### 关键词

元器件检测,FPGA,数智化技术

# Research on FPGA Testing Technology Based on Digital Intelligence

Zhong Yi, Xingyi Li, Hong Zhu, Jianlei Song

Guizhou Aerospace Institute of Measuring and Testing Technology, Guiyang Guizhou

Received: September 15, 2025; accepted: October 13, 2025; published: October 23, 2025

#### **Abstract**

Traditional component testing methods rely on manual visual inspection and single-point functional testing, which have limitations such as high error rates, insufficient coverage, and low efficiency. Especially in the testing of high-density FPGA and SOC chips, the testing cycle and cost have become key bottlenecks restricting equipment delivery. Against this technical predicament, digital and intelligent technologies, relying on the core advantages of data-driven decision-making and intelligent collaborative processing, are gradually reshaping the technological paradigm in the field of

文章引用: 易忠, 李星毅, 朱洪, 宋建磊. 基于数智化的 FPGA 检测技术研究[J]. 软件工程与应用, 2025, 14(5): 1113-1122, DOI: 10.12677/sea.2025.145099

component testing. They are driving the accelerated transformation of this field from the traditional manual-driven model toward the direction of intelligence and digitalization, and the field has currently entered a critical window period for technological iteration. This paper systematically explores the challenges and innovative paths faced by component testing technologies, integrates cutting-edge testing technologies such as machine learning and edge computing, and focuses on studying the intelligent solutions for FPGA testing. Meanwhile, based on the development of component testing technologies, this paper optimizes the current FPGA testing process, aiming to achieve improvements in speed and accuracy in aspects of visual inspection, configuration programs, and test vectors.

### **Keywords**

Component Testing, FPGA, Digital and Intelligent Technologies

Copyright © 2025 by author(s) and Hans Publishers Inc.

This work is licensed under the Creative Commons Attribution International License (CC BY 4.0).

Open Access

#### 1. 引言

电子元器件作为现代信息系统的基石,其质量与可靠性直接决定了装备的性能与寿命,在航空航天、国防装备等关键领域,元器件的微小缺陷都可能会导致灾难性的后果[1]。然而,随着 FPGA、SOC 为代表的高密度复杂器件的广泛应用,传统检测技术面临严峻挑战,传统检测方法依赖人工目检和基于固定配置的单点功能测试,存在测试覆盖率低、精度不足、周期长、成本高等局限,已经成为制约高端装备研发与交付的关键瓶颈[2]。以人工智能、大数据、云计算、物联网和数字孪生为代表的新一代信息技术,正在以前所未有的深度和广度赋能传统产业,推动其从自动化向智能化迈进[3]。在元器件检测领域,利用数据驱动的洞察力和机器智能的决策力,去破解传统测试方法面临的困境,不仅是技术发展的必然趋势,更是保障国家关键领域产业链安全、提升核心竞争力的迫切需求。

本文以 FPGA 作为核心研究对象,旨在系统性地回答如何探索数智化技术与检测的融合路径,构建一套全新、高效、精准、智能的 FPGA 检测范式,既解决当前检测痛点,也为保障关键领域产业链安全、提升检测技术自主可控能力提供支撑。

#### 2. FPGA 检测技术

在 FPGA 的测试流程中,其核心思想是通过施加预设的激励并观察响应,来判断被测器件功能和性能是否符合要求[4]。首先是对外观进行筛选,主要依赖人工目检检查元器件的封装是否有裂纹、引脚是否氧化或变形、丝印是否清晰等。第二是电参数测试,使用仪器(如示波器)在指定条件下测量元器件的静态和动态电学参数,通常 FPGA 需测试电源引脚的静态电流(IDDQ)、输入/输出引脚的电压/电流特性(VIL, VIH, VOL, VOH)、以及关键时钟信号的频率、抖动等,最后是功能测试,旨在验证元器件能否正确执行预先设计的逻辑功能。

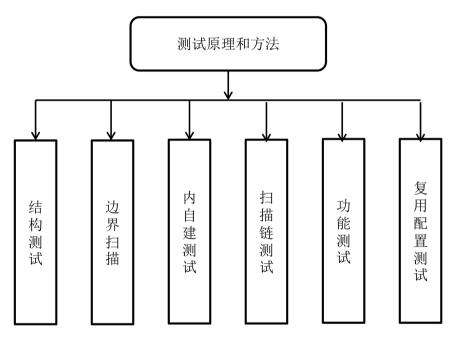

而测试方法分为很多种,包括结构测试、边界扫描、内建自测试等[5],如图 1 所示。

结构测试不关心 FPGA 最终要实现什么功能,而是将其视为一个由逻辑门、触发器、连线等组成的物理结构,旨在发现制造过程中可能引入的物理缺陷。FPGA 内置一个测试访问端口(TAP)和边界扫描寄存器,通过 TAP 控制器,测试系统可以将 FPGA 的每个 I/O 引脚置于测试模式,独立地控制其输出或读

取其输入,从而有效测试芯片与 PCB 板之间的焊接、短路、开路等问题。对于 FPGA 内部规整的、重复性高的模块,如块存储器(BRAM)和 DSP 单元,厂商通常会内置 BIST 电路,用户可以通过特定指令激活 BIST, 让这些模块执行预设的测试算法(如 March 算法),并返回一个简单的测试标志。

常用的方法是内建自测试,可以减少大量的测试向量,通过芯片内部设计的逻辑,芯片能自己完成对某项功能的检测,扫描链多用于 SOC 等不可编程器件,和边界扫描一样是厂家设定的功能,需要特定指令激活[3]。

随着芯片规模和复杂度的指数级增长,对于 FPGA 这类器件来说,覆盖率低、成本高、难以对差错点进行精准定位已经是业内的测试局限所在。中等规模的 FPGA 内部配置位就可能多达数亿个,即使设计上百个测试配置,所能覆盖的实际工作状态和内部节点组合,相对于总体节点组合而言只占据了部分。测试执行所需的 ATE 设备动辄数百万美元,对 ATE 技术人员的要求也很高,芯片更新的快节奏也会带来快速的开发要求,对一颗复杂 FPGA 进行较为全面的多配置测试,耗时可达数分钟甚至更长,测试成本剧增;且 ATE 报告往往只能提供有限的信息,比如某引脚在某时间点的输出值与预期有偏差,但导致这个错误的根本原因是什么只能泛泛分析[6][7]。

因此,数智化检测技术就是解决 FPGA 测试痛点的一把利刃。

Figure 1. Test method diagram 图 1. 测试方法图

#### 3. 基于数智化技术的 FPGA 检测

#### 3.1. 自动化外观检测技术

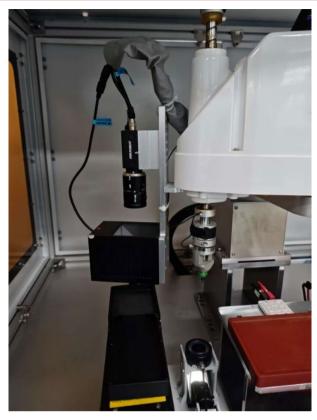

图 2 所示是构建的外观自动化检测平台,可以提高外观检测的速度和精度,外观检测系统包含硬件、软件、驱动三个部分[8] [9]。硬件主要是由 CCD 相机、运动电机、光学显微镜头构成;软件部分是对相机拍摄的相片进行缺陷检测的算法核心,也是人机交互的重要渠道;驱动部分主要是控制步进电机的运动和相机的驱动,完成自动化拍摄过程。缺陷检测算法使用 Yolo v8 神经网络,该算法对表面缺陷检测精度高、速度快。

Figure 2. Component surface defects automatic inspection system diagram 图 2. 元器件表面缺陷自动检测系统图

#### 3.2. 测试向量优化

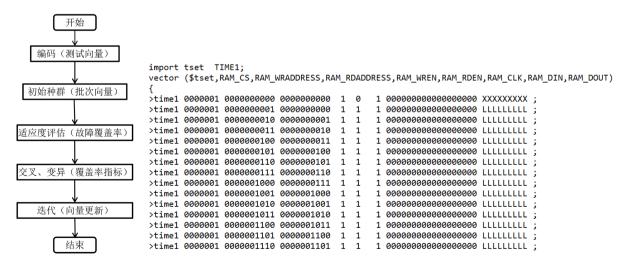

传统功能测试的最大痛点在于测试向量的开发。数智化转型为此提供了全新的解决思路。其核心思想是,将测试向量的生成视为一个数学优化问题,利用机器学习算法来寻找最优解。基于遗传算法的测试向量优化流程如图 3 所示:

Figure 3. Vector optimization flow and RAM-oriented test vectors diagram 图 3. 向量优化流程和 RAM 优化测试向量图

遗传算法的核心思想在于通过多次迭代产生适应度高的后群,在测试向量中,该方法同样适用,但是要进行相应的改动,通过大量的失效数据作为适应度的评价标准,将更容易造成失效的测试向量作为优秀指标来进行迭代,就可以从批量测试数据中得到少量但核心的测试向量,例如在测试 RAM 时候,多采用棋盘数据也是因为大面积跃变更容易得到失效结果,同时也能更全面体现测试覆盖率,同时,最完整的测试应该是对地址和数据都进行遍历,但从向量生成的角度而言是不可能实现的,所以通过基于遗传算法的测试向量优化就可以得到覆盖率更高,相对更全面的测试向量。

方法如下:

- 1) 采用变长二进制编码方案,将测试向量的每一位映射为染色体的"基因",编码长度与被测 FPGA的 RAM 输入宽度动态匹配,例如针对 RAM 位宽为 18的 FPGA,染色体长度设为 18,基因 0 和 1 对应高低电平,随机生成对应位宽的测试向量,构建初始化种群;

- 2) 通过适应度函数(故障覆盖率与测试时间的加权函数)来进行评估:

$$F_{fit} = 0.8 \frac{N_d}{N_c} - 0.2 \frac{T}{T \text{ max}}$$

(1)

其中:  $\frac{N_d}{N_t}$  为故障覆盖率,  $N_d$  是检测故障数,  $N_t$  是故障总数,  $\frac{\mathrm{T}}{\mathrm{Tmax}}$  为测试时间占比。

3) 采用轮盘赌选择法,个体被选中概率与适应度正相关:

$$P_{i} = \frac{F_{fit}}{\sum_{i=1}^{50} F_{fit}}$$

(2)

- 4) 交叉算子采用单点交叉,随机选择交叉点后交换父代染色体片段,交叉概率设为0.75。

- 5) 变异算子采用位变异,对每个基因以 0.01 的概率进行翻转,避免种群早熟。

实验中,随机生成初始种群规模为长度为 16 的共计 50,000 条染色体(测试向量数),最终迭代出 100 组效率和覆盖率最好的测试向量。

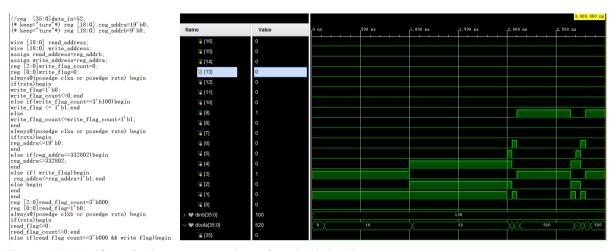

## 3.3. FPGA 测试优化

现有测试机台(如 Teradyne J750、advantest93K)的向量深度都具有一定的局限性,以 J750-HD 为例,最大支持 128 M 深度的向量,该向量指一个工程里测试向量的总和,能满足测试逻辑资源较少的 FPGA,但针对较为复杂的芯片,如赛灵思 7 系列,一个未经过压缩的配置程序向量(串行配置状态)就需要约 50 M 深度的空间,加上覆盖率较高的测试向量,多个测试项的向量深度远远大于 128 M,因此测试流程的优化具有必要性。

整个测试过程中,占据内存空间最大的不是测试向量,而是配置向量。配置向量由 FPGA 的配置程序转换的二进制码流改写而来,测试机台自带的配置软件通常可以充当上位机的角色,如 Teradyne J750中,需在其配置软件 IGXL 中通过 VBT 代码调用 Windows BAT 文件,BAT 文件中通过 TCL 指令写入配置向量。

通过 VBT 代码调用 Windows BAT 文件以写入配置向量的时间花费较大,主要体现在 VIVADO 连接硬件的过程。由于每次写入向量时,TCL 指令调用的过程是独立的,每次都需要重复连接硬件过程。在此基础上,通过一个额外的硬件连接过程的脚本进行写入向量的流程优化:在未进行任何配置向量写入时先运行硬件连接的脚本,再在每个测试项单独向控制台注入下载指令(如图 4 所示),该操作可将向量写入的速度提升三倍以上,在开展的实际测试中,将 700 K 的配置向量文件写入的时间从 25 S/次提升到 6 S/次。

```

# find all ".runs" directory

set runs_folders [glob -directory $script_dir -types d *.runs]

# find all "impl_1" directory in "runs_folders"

set impl_1_folders [glob -directory $runs_folders -types d impl_1]

# find .bit file in "impl_1_folders"

set bit_file [glob -directory $impl_1_folders *.bit]

# connect HW server

@echo on

open_hw

set "bit_dir=%~dp0"

set "bit_file='

connect_hw_server

pause

# auto detect and open the available target

for %%f in ("%bit_dir%*.bit")do(

open_hw_target

set "bit_file=%%f"

goto :found

# enhance the clock frequency to reduce the download time

set_property PARAM.FREQUENCY 12000000 [get_hw_targets]

:found

# program FPGA

echo "PROGRAM_IN_OPEN_HW.tcl">temp.tcl

set hw device [get hw devices]

echo "PROGRAM_DOWNLAND.tcl">>temp.tcl

set_property PROGRAM.FILE $bit_file $hw_device

echo "source temp.tcl"|vivado -mode tcl -source-

program_hw_device $hw_device

puts "success"

echo Successfully download

```

# acquire script directory

set script\_dir [file dirname \$script\_path]

Figure 4. TCL command injection flow diagram 图 4. TCL 指令注入程序图

另外一种方法是通过外接测试板进行配置向量的存储和读取,外接测试板包括一个 epcs 专用存储器及一个用于读取程序的 FPGA 芯片,如图 5 所示,存储器用于存储待测 FPGA 的配置程序,FPGA 芯片通过 IGXL 的指令进行程序的读取并传输到待测的器件上,通过管脚输出二进制配置文件,达到配置待测 FPGA 的目的。

Figure 5. Development board configuring FPGA diagram 图 5. 开发板配置 FPGA 程序图

除了配置程序的下载需要花费大量时间,测试过程中所需要的测试向量大小各异,根据不同模块的

复杂程度有所变化,占用资源多的模块,如 RAM,所需要的测试向量远大于占用资源少的模块,因此对 其测试流程进行优化是很有必要的,通过程序内自建的方式,不仅可以简化流程,也能大大提升测收试 时间,如下图 6 所示,该程序通过接受时钟信号,对内部 RAM 地址进行遍历,并通过多组棋盘和极值数 据对数据进行遍历,通过与寄存器数据进行比对最后将结果输出,大大提升了测试速度。

Figure 6. RAM self-contained test program and waveform simulation diagram 图 6. RAM 内自建测试程序和波形仿真图

# 4. 元器件检测技术的数智化发展趋势

#### 4.1. 数智化的核心内涵

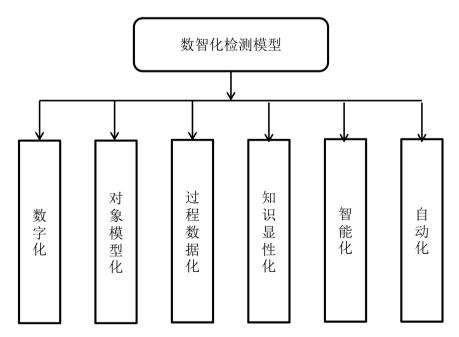

如图 7 所示,数智化技术是一个系统性的范式革命,它包含"数字化"和"智能化"两个紧密相连的层面,共同作用于元器件检测领域,旨在构建一个数据驱动、智能决策的全新检测生态。

Figure 7. Digital intelligent detection model diagram 图 7. 数智化检测模型图

数字化是将元器件检测的全流程、全要素进行数据化表达和网络化连接;对象模型化将被测器件从一个物理实体转变为一个包含其设计数据、行为模型、物理参数的"数据表";过程数据化将测试过程中的每一个环节形成数据;知识显性化是将过去依赖于专家头脑中的隐性知识,通过知识图谱、规则引擎等技术转化为计算机可以理解和执行的显性知识库;智能化、自动化是转型的目标。

#### 4.2. 元器件检测的关键数智化技术

数智化转型由一系列关键技术作为支柱,它们在元器件检测领域的应用,共同构成了技术基石。首先是机器学习,例如通过 CNN 来检测元器件的外观缺陷,通过遗传算法来优化测试向量等,通过数据也能进行性能的预测;其次是大数据技术,可以对海量测试数据分析后进行生产、测试、应用的全流程追溯,智能分析不同的数据差异带来的影响,优化工艺流程,最后是边缘计算技术,将数据在生产线上部署边缘节点,实时分析传感器采集的参数。这些先进的技术也铸就了元器件数字孪生的基础。

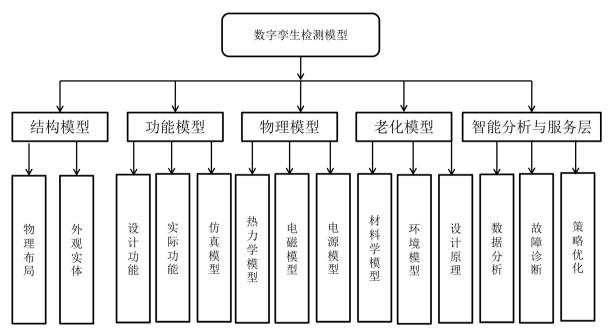

元器件数字孪生技术是一个多模态高融合的模型,如图8所示:

Figure 8. Digital twin model diagram 图 8. 数字孪生模型图

其结构模型精确到晶体管级的网表、物理布局布线信息。功能模型可执行的行为级、RTL级、门级仿真模型。物理模型热力学模型(预测芯片温度分布)、电磁场模型(预测 EMI)、电源网络模型(预测电压降 PDN)。老化模型基于材料科学,模拟器件在长时间工作和压力下(如高温、辐射)的性能退化规律。智能分析与服务层是孪生体的"大脑",是实现价值的核心,它包含了一系列的智能化服务和应用测试仿真服务、故障诊断服务、健康预测服务、测试策略优化服务。

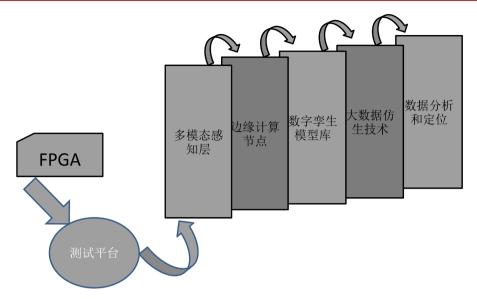

数字孪生体系结构主要由下图 9 所示,测试平台通过对 FPGA 的实时测试,将数据传入云端多模态感知层,再由边缘计算中心连接数字孪生模型库,通过大数据技术进行分析,最后定位测试结果和问题。同时,智能模型也可以将多种不同但适用的配置程序和测试向量用于当前测试的芯片,在接入例如 DEEPSEEK 等大模型后,还能针对测试芯片的资源生成或选用测试程序。

Figure 9. Digital twin architecture diagram 图 9. 数字孪生架构图

通过对不同的 FPGA 进行测试并上传该 FPGA 的生产环境、设计原理、测试环境等数据,结合海量的数据进行大数据分析,从而得到类似生产环境、工作环境、相同构造材料、设计原理情况下,芯片的功能、性能和寿命的检测和预测,并通过不同条件下的测试数据,回环芯片设计 和制造的最优解,同时,对某些特定使用场景下芯片的选型也能提供强有力的支持。

以可靠性寿命评估为例,Arrhenius 模型描述了温度对退化速率的加速作用:

$$K(T) = k_0 e^{-E_a/(k_B T)}$$

(3)

其中,K(T)为退化速率, $k_0$  是否前因子,对不同器件通过实验得到, $E_a$  为激活能, $k_B$  为波尔滋蔓常数,T 为环境温度。

结合负载应力的影响,就可以得到多应力条件下的可靠性寿命预测公式:

$$t_R = \frac{1}{k(T, U)} \ln \frac{\Delta t_{th}}{\Delta t_0} \tag{4}$$

其中, $\Delta t_{t_0}$ 为时序退化的失效阈值, $\Delta t_0$ 为初始退化量。

显然,构建一个繁荣度高的数字孪生体,在未来元器件检测技术的发展中会是一个不可或缺的方向,浙江理工大学的钱萍等人已经构建了基于材料、环境、工艺、性能等多方面融合的单一元器件加速退化试验模型[10],随着技术的发展,相信对不同型号的元器件也会建立起能进行多方面预测的数智化综合应用体。

#### 5. 结语

FPGA 作为多个系统应用的核心元器件,在功能控制、数据计算等方面有着不可或缺的低位,特别是在国防、工业、车规等方面,其性能与可靠性需要通过严谨的 FPGA 测试来保障,在数字化浪潮的推动下,构建 FPGA 数字孪生测试系统,实现测试流程的数字化管控与测试数据的智能分析必然是未来的发展趋势,本文基于目前一些人工智能算法和技术在 FPGA 测试的配置和测试向量上做了一些优化和改进,结合自动化外观测试设备和 ATE 机台 J750 进行实验和分析,旨在缩减大规模 FPGA 测试所需的时间,

并通过优化测试向量提升测试覆盖率。

当前,元器件的检测还没有进入到完全自动化的阶段,但随着技术的发展和科技的革新,元器件检测技术会朝着去人化、机器化、智能化的方向变革,在未来,随着数字孪生等技术的发展,元器件检测技术不仅是验证,更能作为预测手段和设计优化方法。

# 参考文献

- [1] 雷增钰, 曹慧亮, 石云波, 等. 基于伪速度谱的 BGA 芯片冲击失效边界研究[J]. 兵器装备工程学报, 2025, 46(7): 193-199.

- [2] 文玺, 赵中泽, 王伟伟. 电子元器件自动测试技术研究进展[J]. 中文科技期刊数据库(全文版)工程技术, 2021(10): 2

- [3] 郭超. 软件自动化测试技术及其在 GIS 软件测试中的应用研究[J]. 科学大众, 2021(2): 238-239.

- [4] 张昊,周哲帅.基于边界扫描的远程可测性设计技术研究[J].通信技术,2020,53(11):2872-2877.

- [5] 继伟, 杨兵. 边界扫描测试技术综述[J]. 电子世界, 2016(10): 34-36.

- [6] 周中顺, 夏蔡娟, 李连碧, 等. 基于 Chroma 3380P 测试平台的高效 FT 测试方案[J]. 电子与封装, 2025, 25(2): 38-42.

- [7] 许梦龙, 鲁小妹, 赵来钖. 一种优化芯片测试时间的方法[J]. 集成电路应用, 2020, 37(2): 39-41.

- [8] 卢荣胜. 自动光学检测技术的发展现状[J]. 红外与激光程, 2008, 37(S1): 124-127.

- [9] 锦成, 刘鑫, 刘蜜, 等. 电子元器件产品外观质量智能检测技术研究[J]. 仪表技术与传感器, 2020(12): 101-104, 109.

- [10] 钟立强, 陈文华, 钱萍, 等. 基于连续应力与离散应力综合的加速退化试验设计方法研究[J]. 机械工程学报, 2020, 56(2): 201-209.